#### The Network Times

Handbook Series - Part X

# **Deep Learning for Network Engineers**

Understanding Traffic Patterns and Network Requirements in the Al Data Center

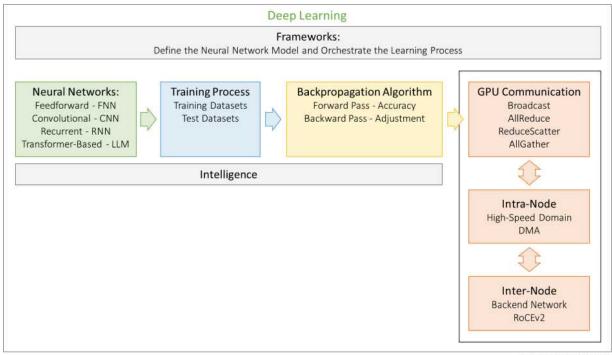

Deep Learning uses Deep Neural Network (DNN) models to predict accurate outputs based on input data. To achieve reliable predictions, test datasets are run through the DNN over multiple iterations, during which model parameters are adjusted to improve performance. In large-scale training clusters, this process generates massive "elephant flows" between workers, requiring a high-speed, lossless transport network. Communication between workers may leverage intra-server high-speed NVLinks or an Ethernet-based backend network for inter-node traffic. This book not only explains Deep Learning processes but also explores how to design and build the high-performance backend networks needed to support them.

#### The Network Times

Handbook Series – Part X

Deep Learning for Network Engineers Understanding Traffic Patterns and Network Requirements in the AI Data Center

Toni Pasanen, CCIE#28158

Copyright © Toni Pasanen, all rights reserved.

First Edition - 18 May 2025

Special thanks to **Magnus Ekman** for publishing the incredible book:

Learning Deep Learning: Theory and Practice of Neural Networks, Computer Vision, Natural Language Processing, and Transformers Using TensorFlow, (17 Aug. 2021).

It was my primary reference when writing the Deep Learning chapters, which is why it's listed as the first source in Chapters 1–7.

This book is dedicated to my tiny black dog, who took me for long walks away from the computer—four to five times every day. And who graciously agreed to let me use her pretty face on the cover of my book once again, making this book not just mine, but ours.

# ABOUT THE AUTHOR

Toni Pasanen, CCIE No. 28158 (Routing & Switching), is a Principal Network Architect and Distinguished Engineer at Fsas Technologies. He specializes in data center networking, including both traditional switched networks and modern BGP EVPN/VXLAN Clos fabrics, as well as AI data centers. In addition to on-premises data center networking, Toni is also an expert in cloud networking, particularly in Microsoft Azure and Amazon Web Services (AWS).

Although his current focus is on AI data center solutions, Toni has designed and implemented a wide range of networks across other domains, including MPLS-based WANs and data centers (e.g., MPLS-VPLS). He has also taught network technologies, such as Routing, Switching, MPLS, and QoS, while working for an official Cisco Learning Partner.

Since 2019, Toni has authored ten books on network technologies:

Virtual Extensible LAN – VXLAN:

A Practical Guide to VXLAN Solution,

August 2019

## LISP Control-Plane in Campus Fabric:

A Practical Guide to Understand the Operation of Campus Fabric,

February 2020

#### VXLAN Fabric with BGP EVPN Control-Plane:

Design Considerations,

September 2020

### Object-Based Approach to Cisco ACI:

The Logic Behind the Application Centric Infrastructure,

December 2020.

#### Cisco SD-WAN:

A Practical Guide to Understand the Basics of Cisco Viptela Based SD-WAN Solution, May 2021.

#### Network Virtualization:

LISP, OMP, and BGP EVPN Operation and Interaction,

August 2021.

## AWS Networking Fundamentals:

A Practical Guide to Understand How to Build a Virtual Datacenter into the

AWS Cloud,

January 2021.

## Azure Networking Fundamentals:

A Practical Guide to Understand How to Build a Virtual Datacenter into the Azure Cloud,

August 2022.

# Azure Networking Handbook:

A Comprehensive Guide to Help You Step into the World of Azure Networking, August 2023.

## Deep Learning for Network Engineer:

Understanding Traffic Patterns and Network Requirements in the AI Data Center,

May 2025.

# ABOUT THIS BOOK

Several excellent books have been published over the past decade on Deep Learning (DL) and Datacenter Networking. However, I have not found a book that covers these topics together—as an integrated deep learning training system—while also highlighting the architecture of the datacenter network, especially the backend network, and the demands it must meet. This book aims to bridge that gap by offering insights into how Deep Learning workloads interact with and influence datacenter network design.

# SO, WHAT IS DEEP LEARNING?

Deep Learning is a subfield of Machine Learning (ML), which itself is a part of the broader concept of Artificial Intelligence (AI). Unlike traditional software systems where machines follow explicitly programmed instructions, Deep Learning enables machines to learn from data without manual rule-setting.

At its core, Deep Learning is about training artificial neural networks. These networks are mathematical models composed of layers of artificial neurons. Different types of networks suit different tasks—Convolutional Neural Networks (CNNs) for image recognition, and Large Language Models (LLMs) for natural language processing, to name a few.

Training a neural network involves feeding it labeled data and adjusting its internal parameters through a process called backpropagation. During the forward pass, the model makes a prediction based on its current parameters. This prediction is then compared to the correct label to calculate an error. In the backward pass, the model uses this error to update its parameters, gradually improving its predictions. Repeating this process over many iterations allows the model to learn from the data and make increasingly accurate predictions.

## WHY SHOULD NETWORK ENGINEERS CARE?

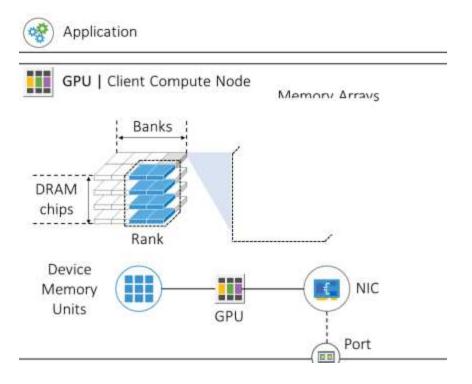

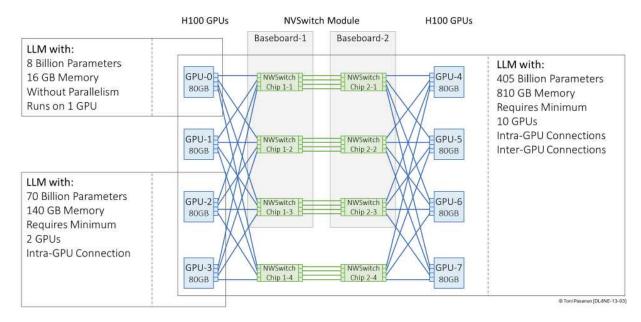

Modern Deep Learning models can be extremely large, often exceeding the memory capacity of a single GPU or CPU. In these cases, training must be distributed across multiple processors. This introduces the need for highspeed communication between GPUs—both within a single server (intranode) and across multiple servers (inter-node).

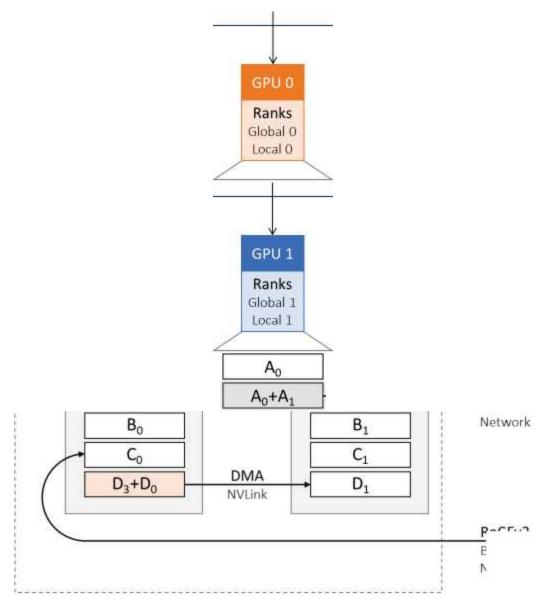

Intra-node GPU communication typically relies on high-speed interconnects like NVLink, with Direct Memory Access (DMA) operations enabling efficient data transfers between GPUs. Inter-node communication, however, depends on the backend network, either InfiniBand or Ethernet-based. Synchronization of model parameters across GPUs places strict requirements on the network: high throughput, ultralow latency, and zero packet loss. Achieving this in an Ethernet fabric is challenging but possible.

This is where datacenter networking meets Deep Learning. Understanding how GPUs communicate and what the network must deliver is essential for designing effective AI data center infrastructures.

©Toni Pasanen (DL4NE-About The Book)

## WHAT THIS BOOK IS-AND ISN'T

This book provides a theoretical and conceptual overview. It is not a configuration or implementation guide, although some configuration examples are included to support key concepts. Since the focus is on the Deep Learning process, not on interacting with or managing the model, there are no chapters covering frontend or management networks. The storage network is also outside the scope. The focus is strictly on the backend network.

The goal is to help readers—especially network professionals—grasp the "big picture" of how Deep Learning impacts data center networking.

## ONE FINAL NOTE

In all my previous books, I've used font size 10 and single line spacing. For this book, I've increased the font size to 11 and the line spacing to 1.15. This wasn't to add more pages but to make the reading experience more comfortable. I've also tried to ensure that figures and their explanations appear on the same page, which occasionally results in some white space.

I hope you find this book helpful and engaging as you explore the fascinating intersection of Deep Learning and Datacenter Networking.

# HOW THIS BOOK IS ORGANIZED

# PART I – CHAPTERS 1-8: DEEP LEARNING AND DEEP NEURAL NETWORKS

This part of the book lays the theoretical foundation for understanding how modern AI models are built and trained. It introduces the structure and purpose of artificial neurons and gradually builds up to complete deep learning architectures and parallel training methods.

Artificial Neurons and Feedforward Networks (Chapters 1 - 3)

The journey begins with the artificial neuron, also known as a perceptron, which is the smallest functional unit of a neural network. It operates in two key steps: performing a matrix multiplication between inputs and weights, followed by applying a non-linear activation function to provide an output.

By connecting many neurons across layers, we form a Feedforward Neural Network (FNN). FNNs are ideal for basic classification and regression tasks and provide the stepping stone to more advanced architectures.

Specialized Architectures: CNNs, RNNs, and Transformers (Chapters 3 - 9)

After covering FNNs, this part dives into models designed for specific data types:

- Convolutional Neural Networks (CNNs): Optimized for spatial data like images, CNNs use filters to extract local features such as edges, textures, and shapes, while keeping the model size efficient through weight sharing.

- Recurrent Neural Networks (RNNs): Designed for sequential data like text and time series, RNNs maintain a hidden state that captures previous input history. This allows them to model temporal dependencies and context across sequences.

- Transformer-based Large Language Models (LLMs): Unlike RNNs, Transformers use self-attention mechanisms to weigh relationships between all tokens in a sequence simultaneously. This architecture underpins state-of-the-art language models and enables scaling to billions of parameters.

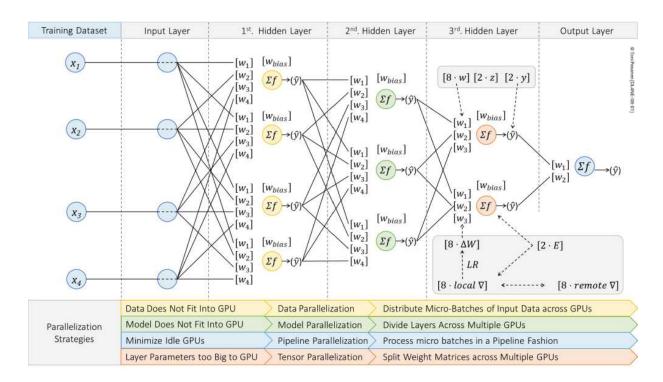

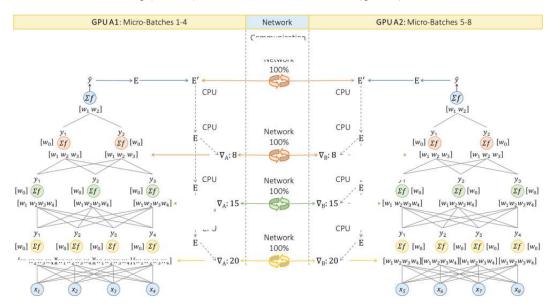

Parallel Training and Scaling Deep Learning (Chapter 8)

As models and datasets grow, training them on a single GPU becomes impractical. This section explores the three major forms of distributed training:

- Data Parallelism: Each GPU holds a replica of the model but processes different mini-batches of input data. Gradients are synchronized at the end of each iteration to keep weights aligned.

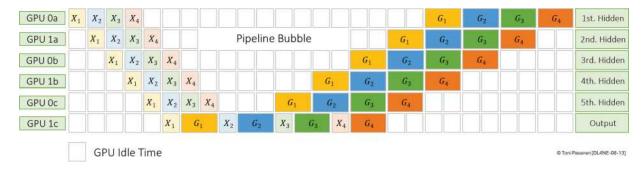

- Pipeline Parallelism: The model is split across multiple GPUs, with each GPU handling one stage of the forward and

backward pass. Micro-batches are used to keep the pipeline full and maximize utilization.

• Tensor (Model) Parallelism: Very large model layers are broken into smaller slices, and each GPU computes part of the matrix operations. This approach enables the training of ultra-large models that don't fit into a single GPU's memory.

# PART II – CHAPTERS 9 – 14: AI DATA CENTER NETWORKING

This part of the book focuses on the network technologies that enable distributed training at scale in modern AI data centers. It begins with an overview of GPU-to-GPU memory transfer mechanisms over Ethernet and then moves on to congestion control, load balancing strategies, network topologies, and GPU communication collectives.

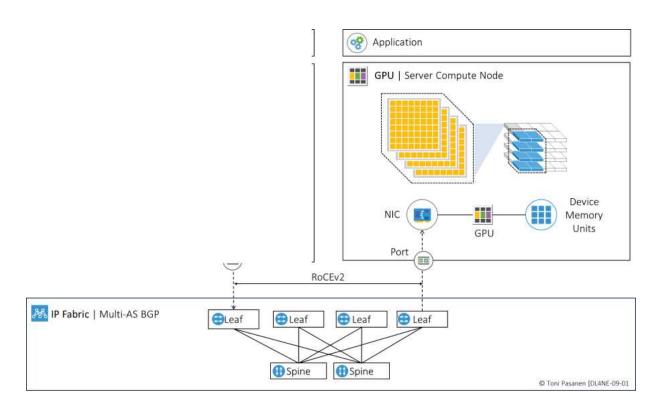

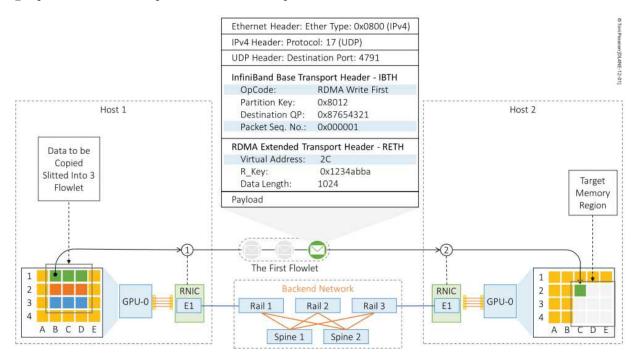

RoCEv2 and GPU-to-GPU Transfers (Chapter 9)

The section starts by explaining how Direct Memory Access (DMA) is used to copy data between GPUs across Ethernet using RoCEv2 (RDMA over Converged Ethernet version 2). This method allows GPUs located in different servers to exchange large volumes of data without CPU involvement.

DCQCN: Data Center Quantized Congestion Notification (Chapters 10 - 11)

RoCEv2's performance depends on a lossless transport layer, which makes congestion management essential. To address this, DCQCN provides an advanced congestion control mechanism. It dynamically adjusts traffic flow based on real-time feedback from the network to minimize latency and packet loss during GPU-to-GPU communication.

- Explicit Congestion Notification (ECN): Network switches mark packets instead of dropping them when congestion builds. These marks trigger rate adjustments at the sender to prevent overload.

- Priority-based Flow Control (PFC): PFC ensures that traffic classes like RoCEv2 can pause independently, preventing buffer overflows without stalling the entire link.

Load Balancing Techniques in AI Traffic (Chapter 12)

In addition to congestion control, effective load distribution is critical for sustaining GPU throughput during collective communication. This section introduces several techniques used in modern data center fabrics:

- Flow-based Load Balancing: Assigns entire flows or flowlets to paths based on real-time link usage or hash-based distribution, improving path diversity and utilization.

- Flowlet Switching: Divides a flow into smaller timeseparated bursts ("flowlets") that can be load-balanced independently without reordering issues.

- Packet Spraying: Distributes packets belonging to the same flow across multiple available paths, helping to avoid link-level bottlenecks.

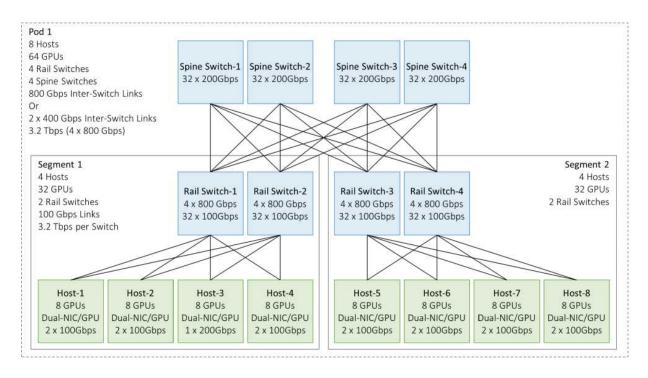

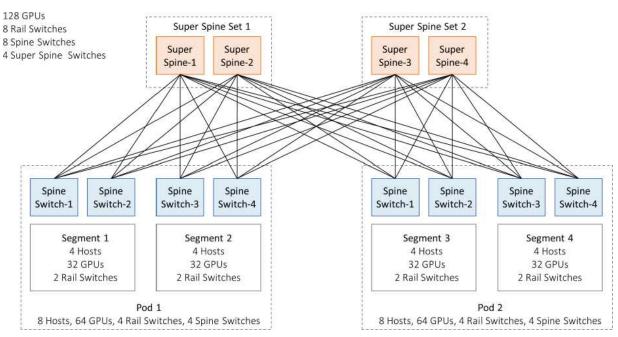

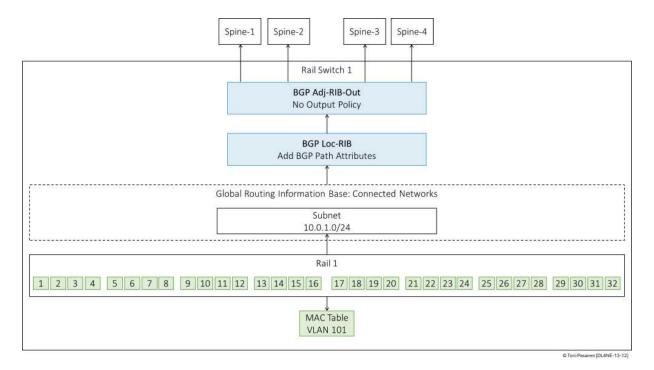

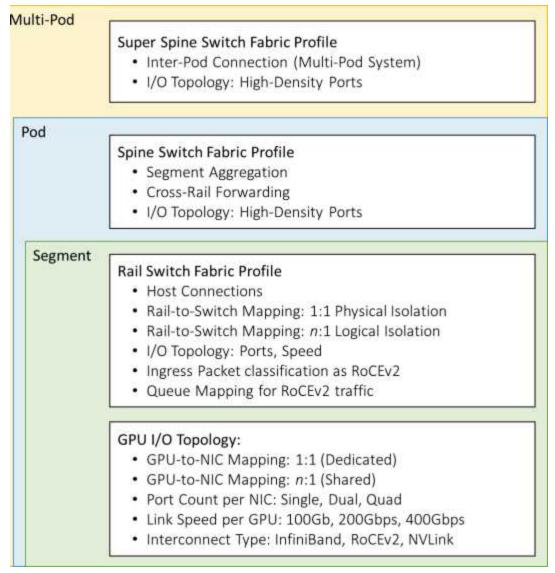

AI Data Center Network Topologies (Chapter 13)

Next, the section discusses design choices in the East-West fabric—the internal network connecting GPU servers. It

introduces topologies such as:

- Top-of-Rack (ToR): Traditional rack-level switching used to connect servers within a rack.

- Rail and Rail-Optimized Designs: High-throughput topologies tailored for parallel GPU clusters. These layouts improve resiliency and throughput, especially during bursty communication phases in training jobs.

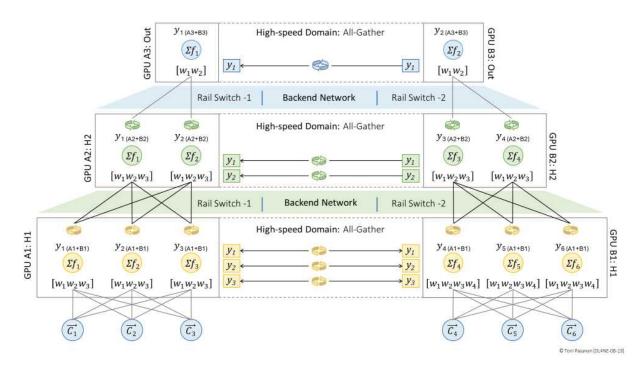

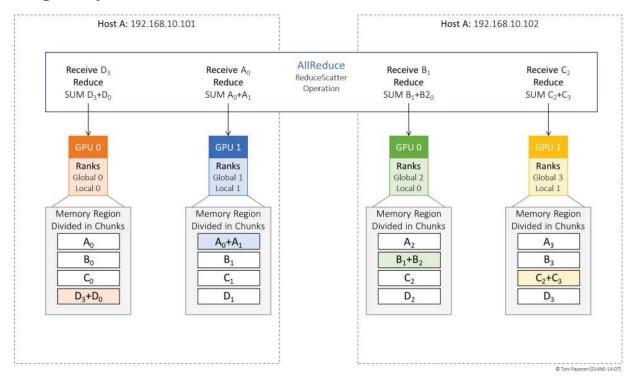

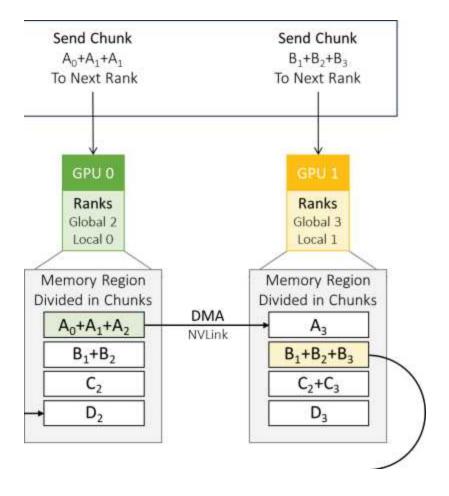

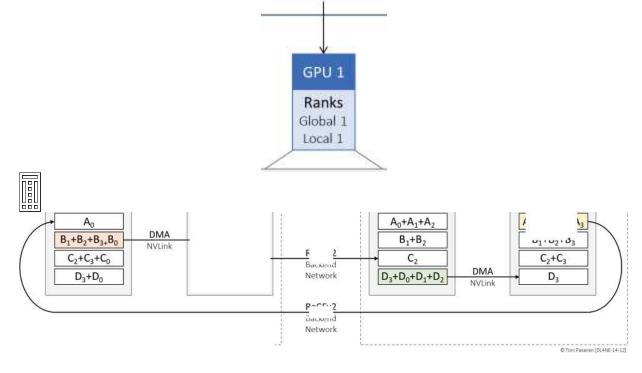

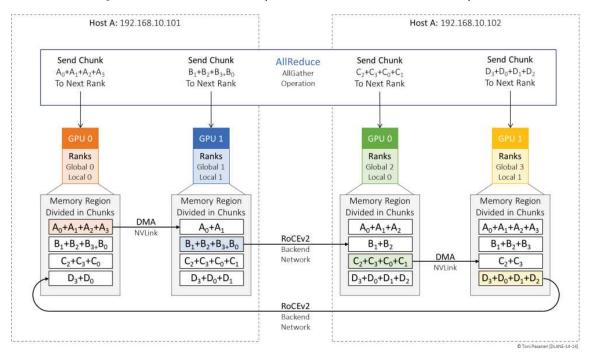

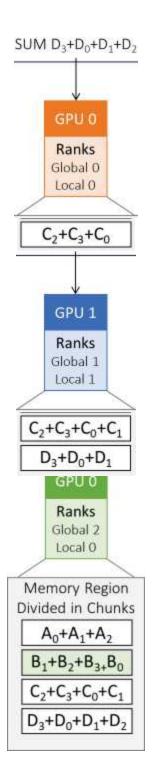

GPU-to-GPU Communication (Chapter 14)

The part concludes with a practical look at collective communication patterns used to synchronize GPUs across the network. These collectives are essential for distributed training workloads:

- AllReduce: Each GPU contributes and receives a complete, aggregated copy of the data. Internally, this is implemented in two phases:

- 1. ReduceScatter: GPUs exchange partial results and compute a portion of the final sum.

- 2. AllGather: Each GPU shares its computed segment so that every GPU receives the complete aggregated result.

- Broadcast: A single GPU (often rank o) sends data—such as communication identifiers or job-level metadata—to all other GPUs at the start of a training job.

## **TARGET AUDIENCE**

I wrote this book for professionals working in the data center networking domain—whether in architectural, design, or specialist roles. It is especially intended for those who are already involved in, or are preparing to work with, the unique demands of AI-driven data centers. As AI workloads reshape infrastructure requirements, this book aims to provide the technical grounding needed to understand both the deep learning models and the networking systems that support them.

# **DISCLAIMERS**

The content of this book is based solely on the author's personal experience, research, and testing. It has not been reviewed, validated, or endorsed by Cisco, NVIDIA, or any other organization or individual. This book is not intended to serve as a design or implementation guide. Readers are encouraged to perform their own validation and testing before applying any of the concepts or techniques in a production environment.

# TABLE OF CONTENTS

About the Author iv

About This Book vi

So, what is Deep Learning? vi

Why should network engineers care? vii

What this book is—and isn't viii

One final note ix

How this book is organized x

Part I – Chapters 1-8: Deep Learning and Deep Neural Networks x

Part II – Chapters 9 – 14: AI Data Center Networking xii

Target Audience xv

Disclaimers xv

Table of Contents xvi

Chapter 1: Artificial Neuron 1

Introduction 1

Artificial Neuron 3

Weighted Sum and Activation Function 4

Bias term 8

**ReLU** Activation Function 10

Network Impact 11

Summary 12

References 13

Chapter 2: Backpropagation Algorithm 15

Introduction 15

Forward Pass 16

Learning Rate 19

Backward Pass 20

Partial Derivative for Error Function – Output Error 21

Partial Derivative for the Activation Function 23

Error Term for Neurons 23

Gradient Calculation 24

Weight Adjustment 26

The Second Iteration - Forward Pass 26

Network Impact 28

### References 30

#### Chapter 3: Multi-Class Classification 31

Introduction 31

MNIST Dataset 31

Forward Pass 33

Model Probability 33

Cross-Entropy Loss 35

Backward Pass 36

**Gradient Computing 36**

Weight Adjustment Values 37

Weight Update 38

References 41

### Chapter 4: Convolutional Neural Networks 43

Introduction 43

Convolution Layer 44

Convolution Process 44

MaxPooling 48

The First Convolution Layer: Convolution 48

The First Convolution Layer: MaxPooling 51

The Second Convolution Layer 52

Fully Connected Layers 53

**Backpropagation Process 53**

References 55

Chapter 5: Recurrent Neural Networks 57

Introduction 57

Text Datasets 58

Training Recurrent Neural Networks 59

Weight Matrices in RNNs 59

Weighted Sum Calculation in the Hidden Layer 59

Output Layer Operations 60

Comparison with Feed-Forward Neural Networks (FNNs) 61

Moving to the Second Time Step 61

Backward Pass in Recurrent Neural Networks 61

Challenges of a RNN Modell 62

Saturated Neurons 64

References 68

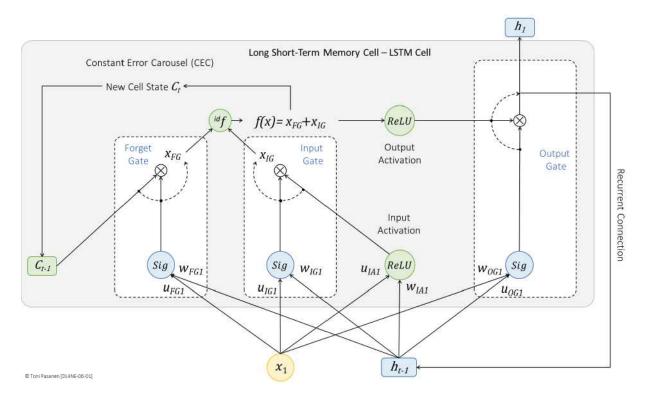

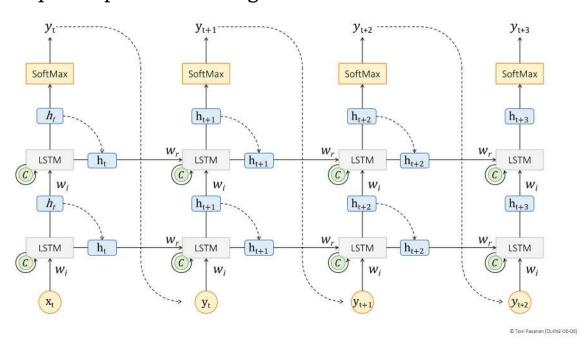

Chapter 6: Long Short-Term Memory 69

Introduction 69

LTSM cell operation 71

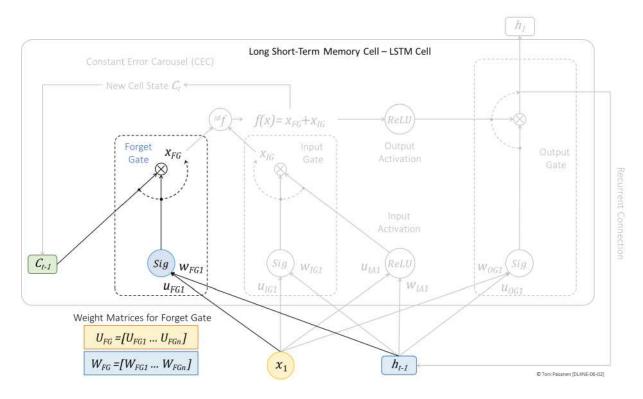

Forget Gate 71

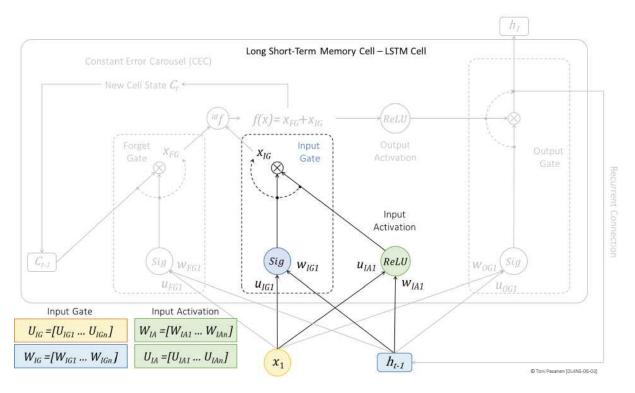

Input Gate 73

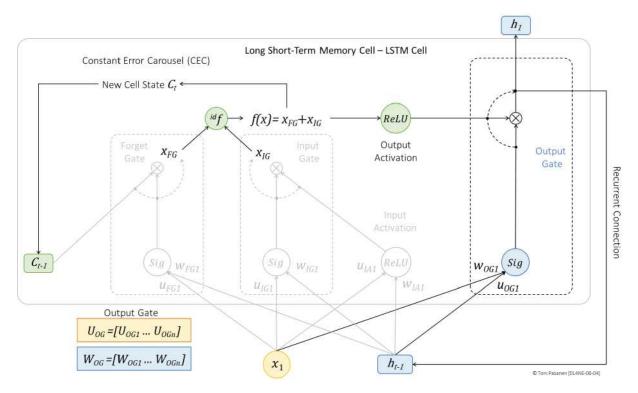

Output Gate 74

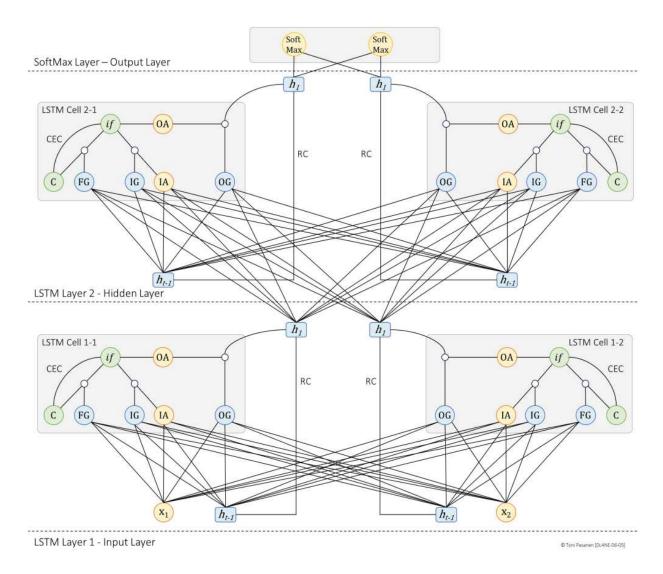

LTSM-based Recurrent Neural Network 75

Recap of the Operation of an LSTM Cell 75

An Overview of an LSTM-Based RNN 76

Conclusion 79

References 80

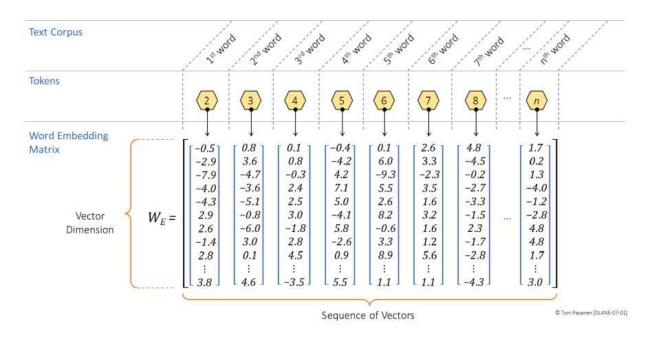

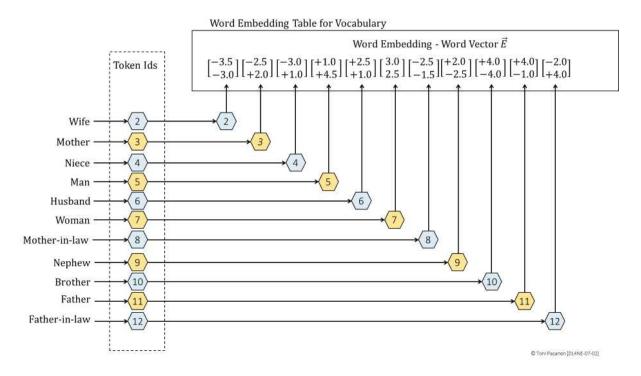

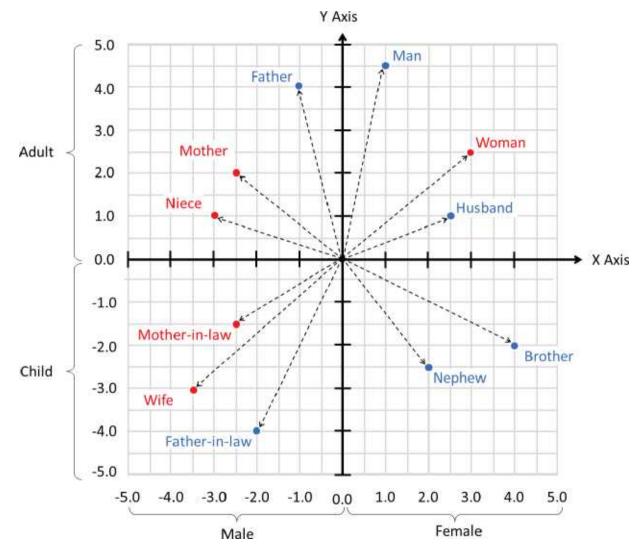

Chapter 7: Large Language Model (LLM) 81

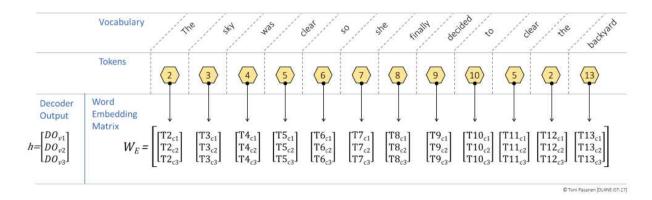

Introduction 81

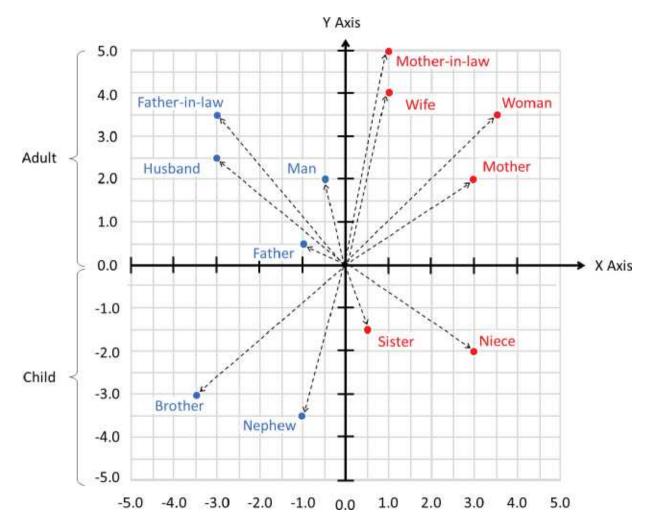

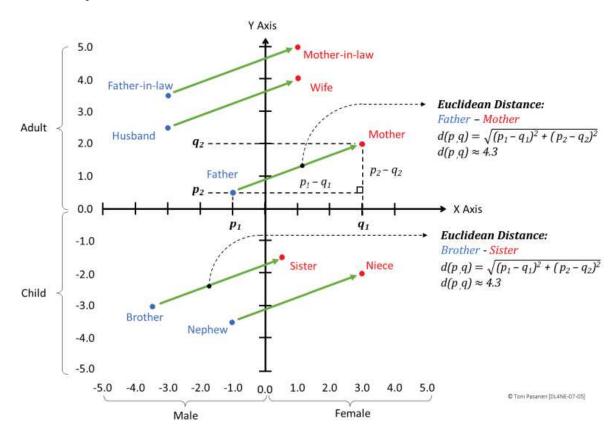

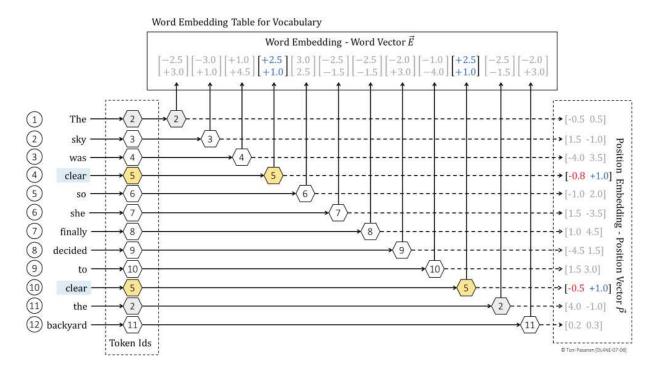

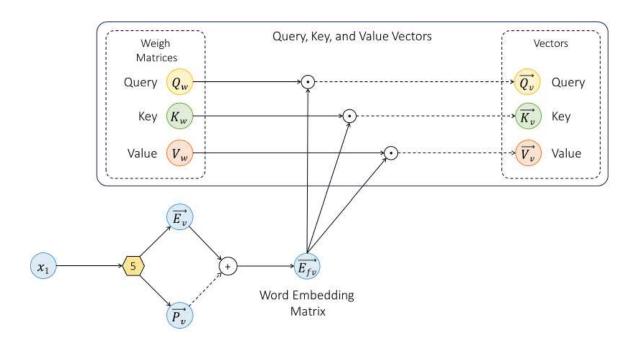

Tokenizer and Word Embedding Matrix 81

Word Embedding 83

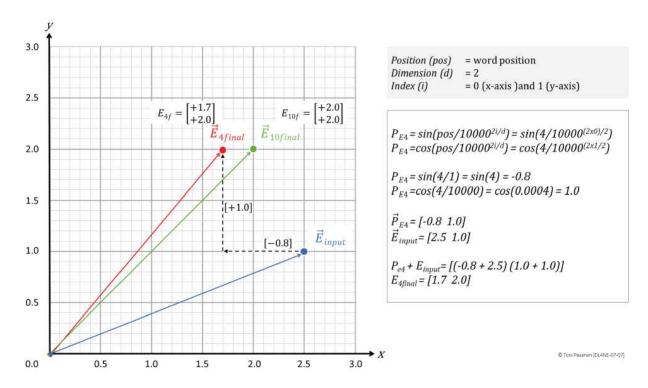

Positional Embeddings 87

Calculating the Final Word Embedding 88

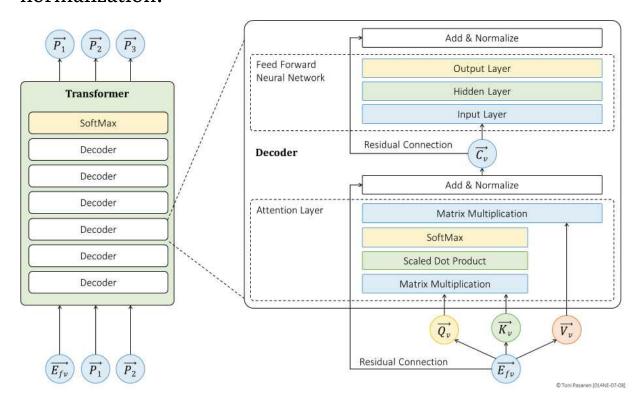

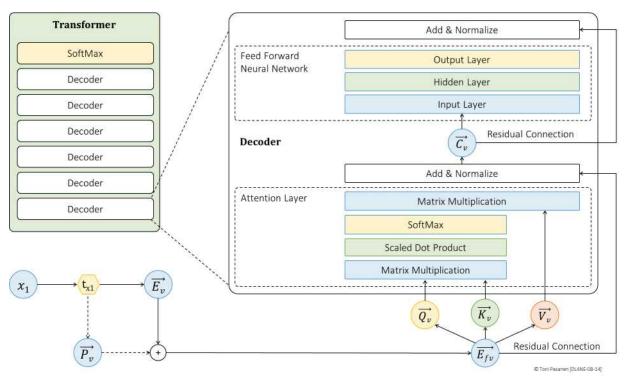

Transformer Architecture 90

Introduction 90

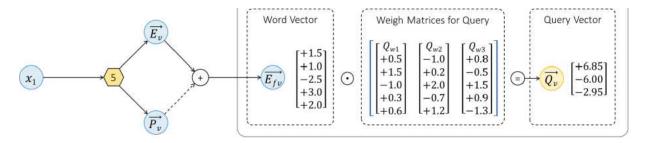

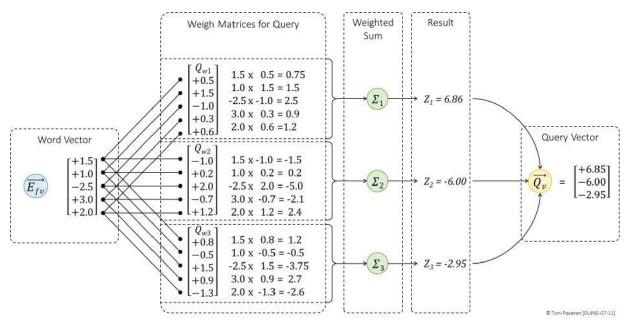

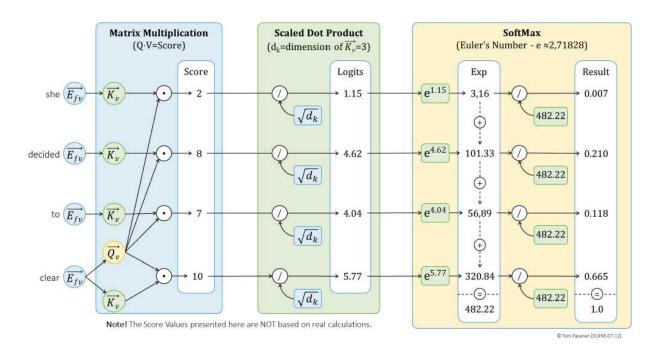

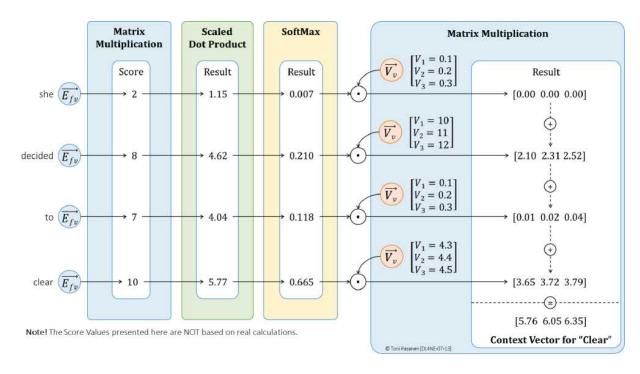

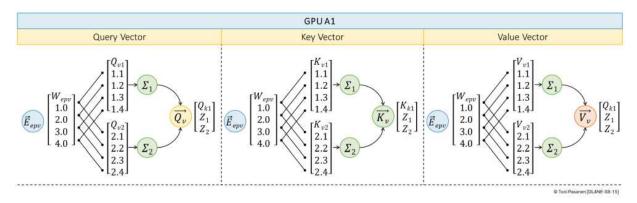

Query, Key and Value Vectors 92

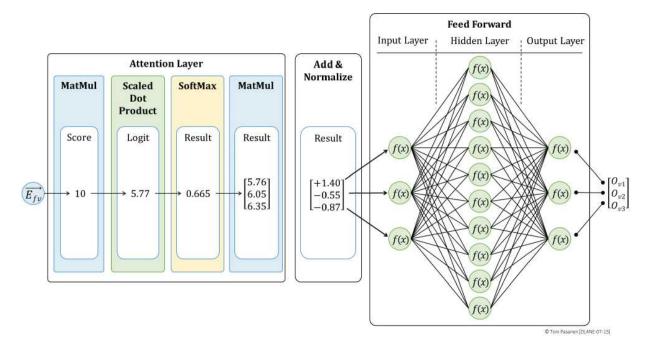

Attention Layer 94

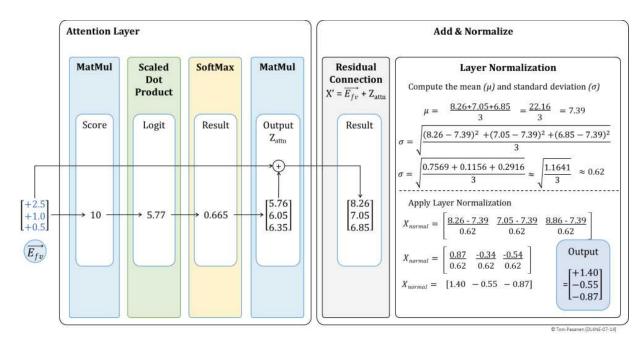

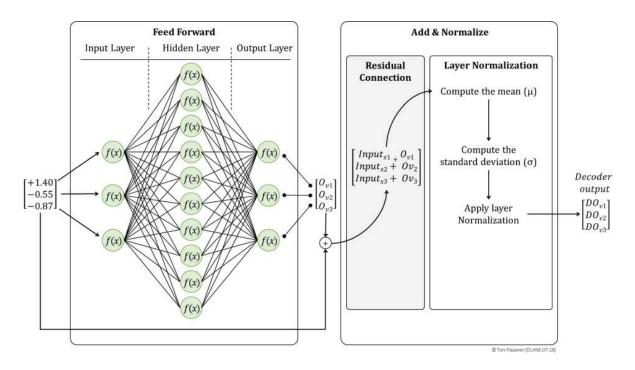

Add & Normalization 96

Feed Forward Neural Network 97

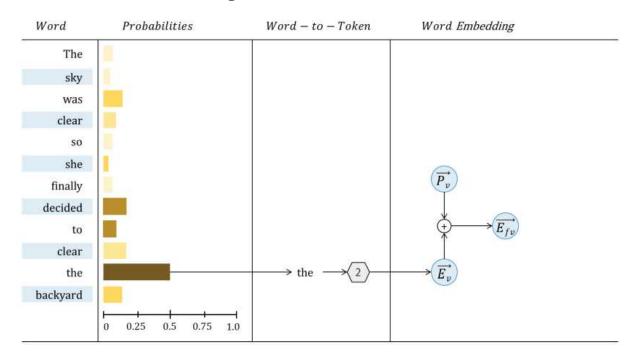

Next Word Probability Computation – SoftMax Function 98

Conclusion 102

References 103

Chapter 8: Parallelism Strategies in Deep Learning 105

Introduction 105

Data Parallelism 106

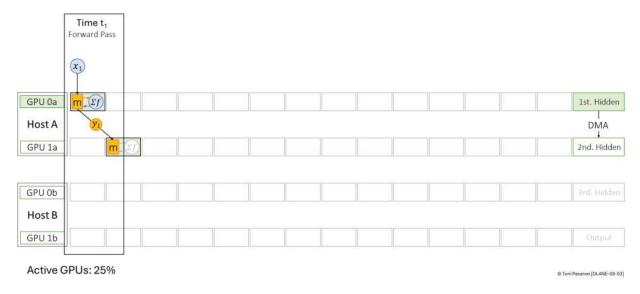

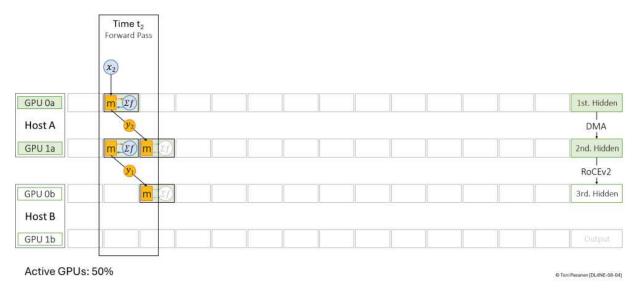

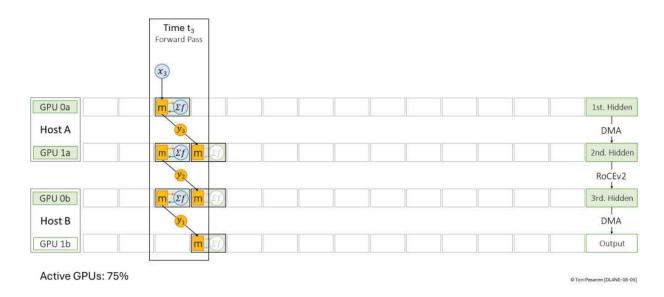

Model Parallelism with Pipeline Parallelism 108

1<sup>st</sup>. Time Step — Active GPUs: 25% - Idle GPUs: 1a, ob, 1b 109

2<sup>nd</sup>. Time Step — Active GPUs: 50% - Idle GPUs: ob, 1b 110

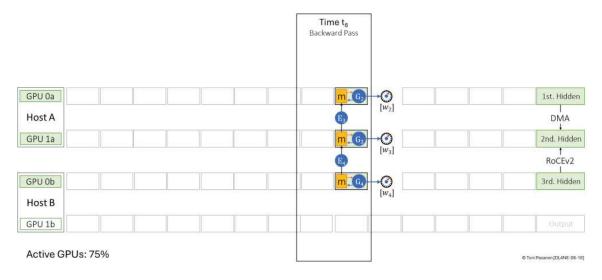

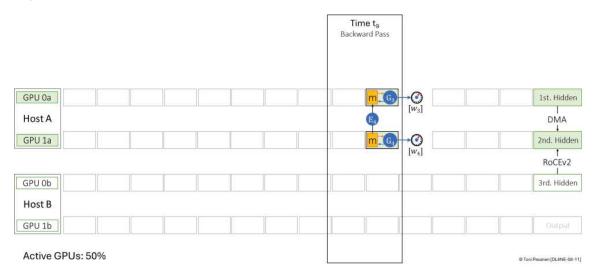

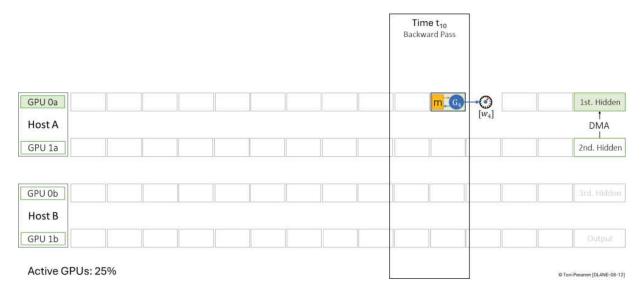

3<sup>rd</sup>. Time Step— Active GPUs: 75% - Idle GPUs: 1b 111

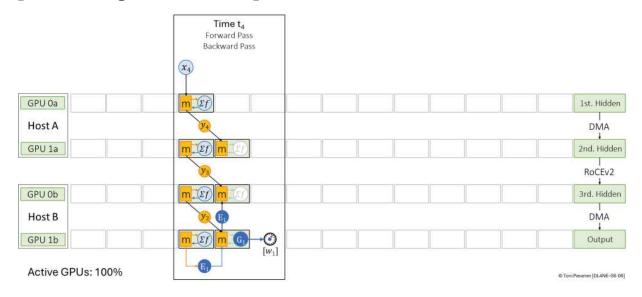

4<sup>th</sup>. Time Step— Active GPUs: 100% - Idle GPUs: none 112

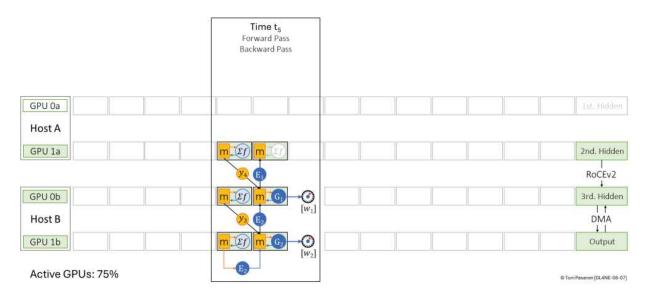

5<sup>th</sup>. Time Step — Active GPUs: 75% - Idle GPUs: 0a 113

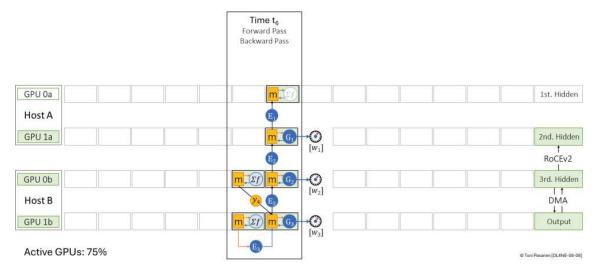

6<sup>th</sup>. Time Step — Three Active GPUs, One Idle GPU: Overall GPU Utilization 75% 114

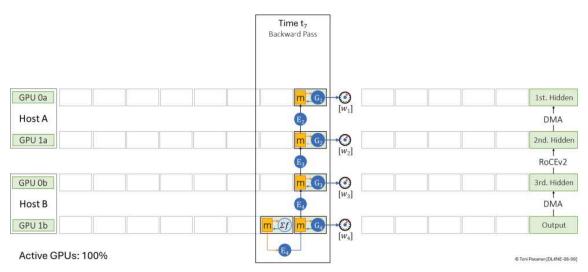

7<sup>th</sup>. Time Step — Four Active GPUs: Overall GPU Utilization 100%

8<sup>th</sup>. Time Step — Three Active GPUs: One Idle GPU: Overall GPU Utilization 75% 115

9<sup>th</sup>. Time Step — Two Active GPUs: Two Idle GPUs: Overall GPU Utilization 50% 116

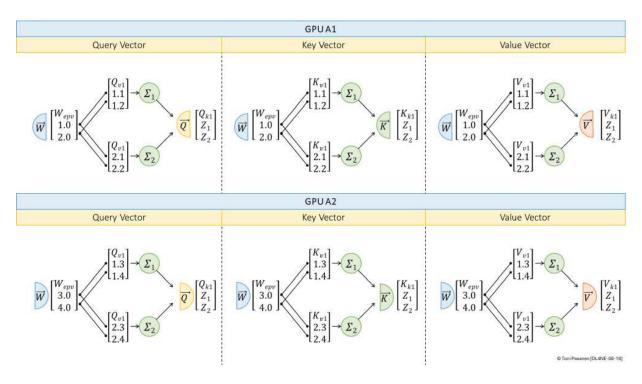

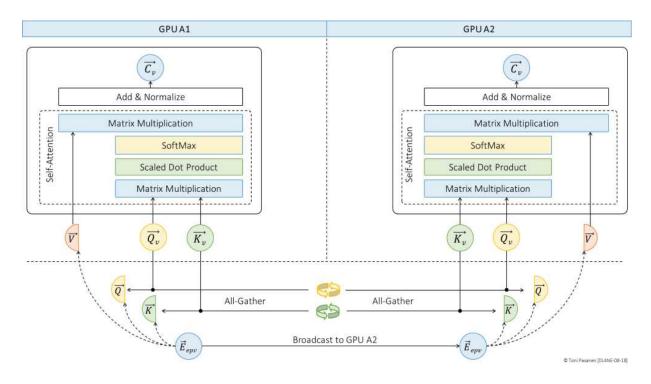

10<sup>th</sup>. Time Step — One Active GPU: three Idle GPUs: Overall GPU Utilization 25% 116 Tensor Parallelism 117

Self-Attention Layer 119

Feedforward Layer 122

Backpropagation 123

References 127

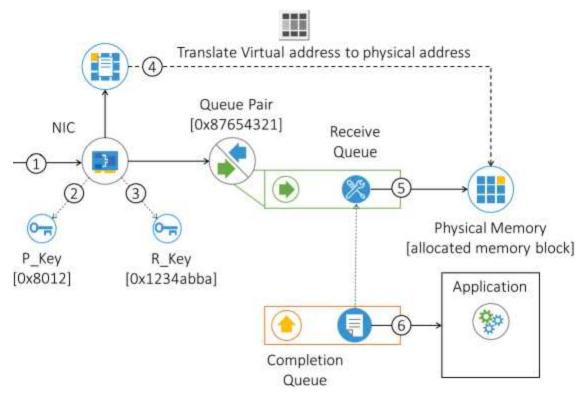

Chapter 9: RDMA Basics 129

Introduction 129

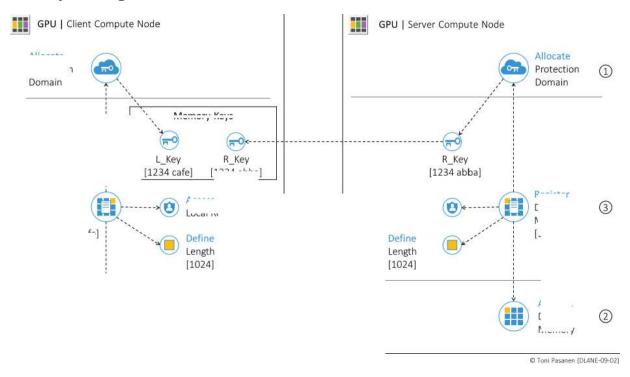

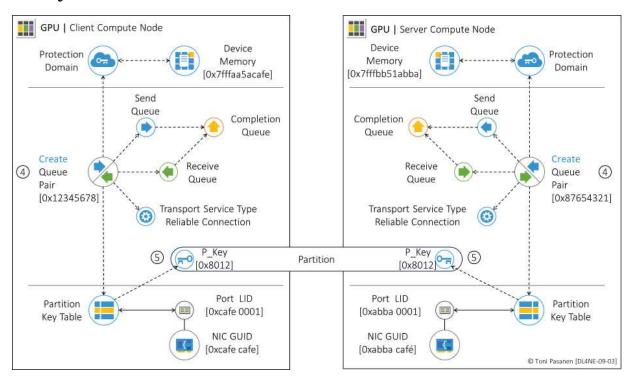

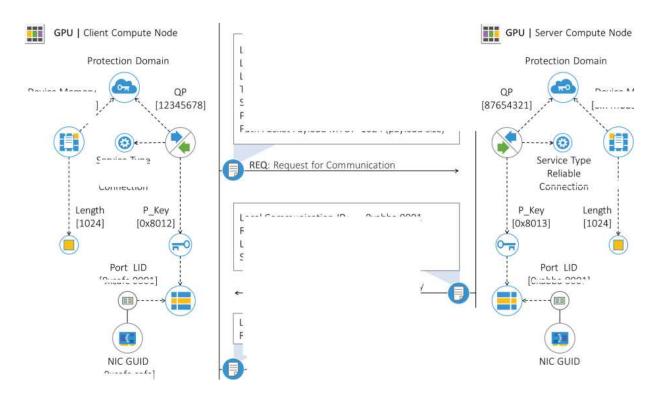

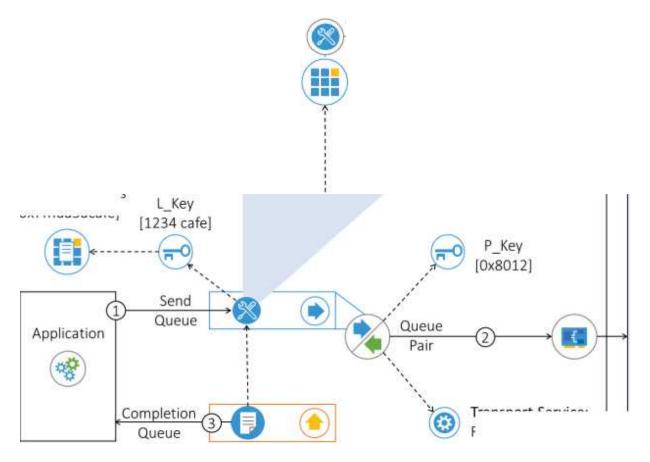

An overview of RDMA Processes 130

Memory Allocation and Registration 131

Create Queue Pairs 132

RDMA Connection Initiation 134

Work Request Message 135

References 138

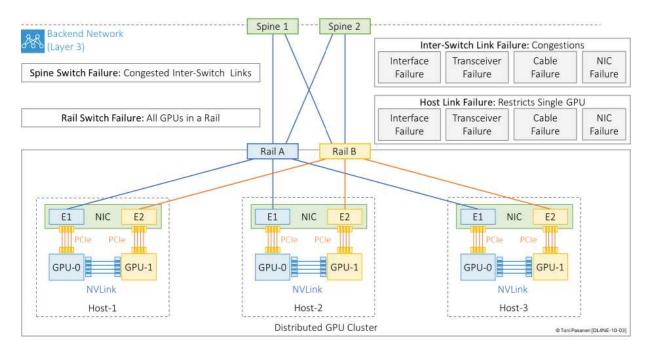

Chapter 10: Challenges in AI Fabric Design 139

Introduction 139

Egress Interface Congestions 140

Single Point of Failure 141

Head-of-Line Blocking 143

Hash-Polarization with ECMP 144

References 146

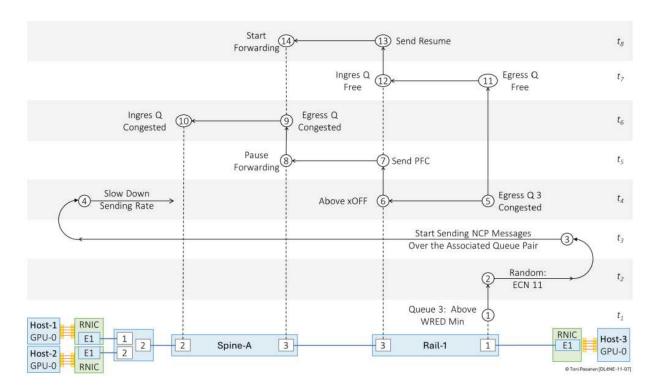

Chapter 11: Congestion Avoidance 147

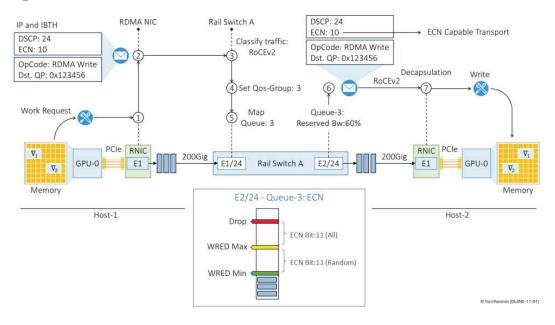

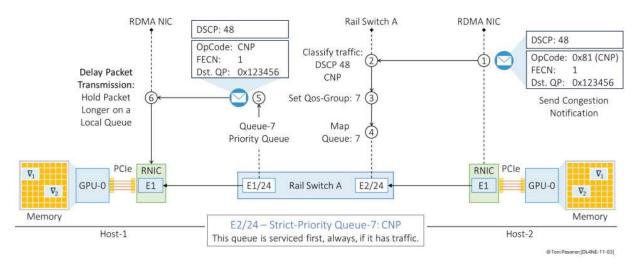

GPU-to-GPU RDMA Write Without Congestion 148

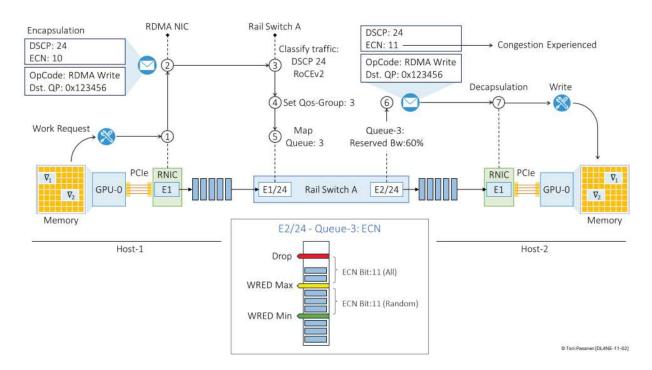

Explicit Congestion Notification -ECN 149

DSCP-Based Priority Flow Control (PFC) 153

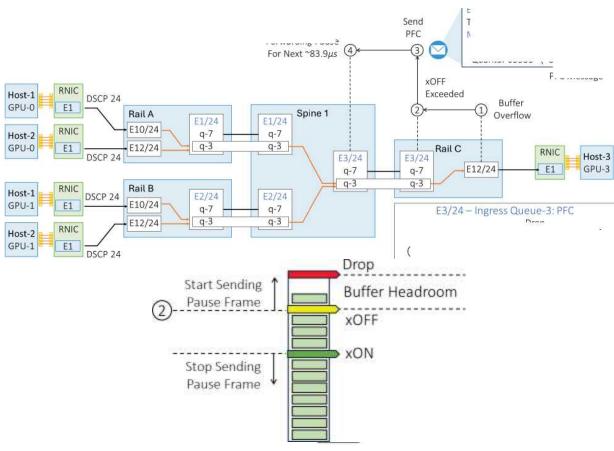

Step 1: Buffer Overflow on Rail Switch C (Egress to GPU-3, Host 3) 154

Step 2: xOFF Threshold Exceeded 155

Step 3: Generating a PFC Pause Frame (MAC Control Frame) 155

Step 4: Spine Switch 1 Pauses Transmission on Priority Queue 3 156

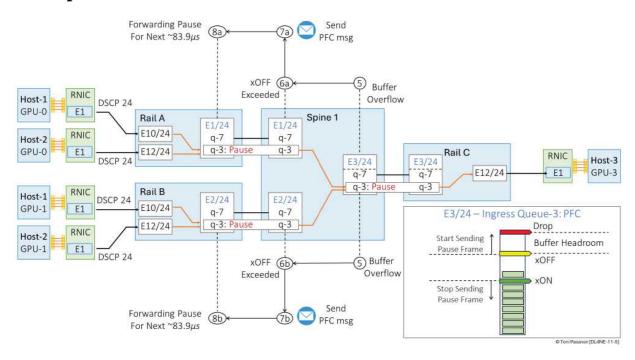

Step 5: Congestion on Spine Switch 1 Egress Queue to Rail Switch C 157

Step 6: xOFF Threshold Exceeded on Spine Switch 1 Ingress Interfaces 158

Step 7: Spine Switch 1 Sends PFC Pause Frames to Rail Switch A and B 158

Step 8: Rail Switches A and B Pause Queue 3 Traffic to Spine Switch 1158

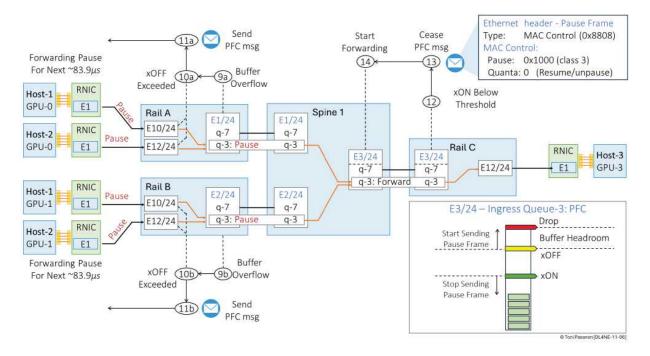

Steps 9a – 14: Downstream Resume and Congestion Recovery 159

LLDP with DCBX 161

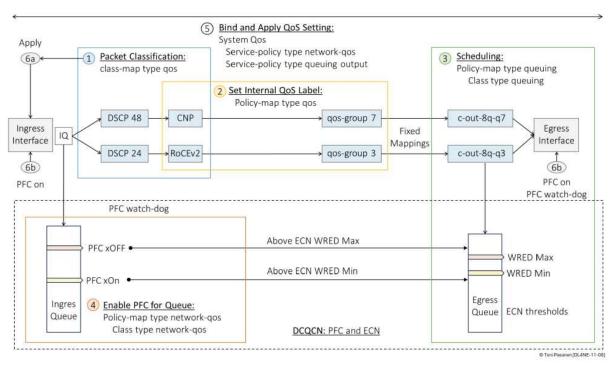

Data Center Quantized Congestion Notification (DCQCN) 162

How DCQCN Combines ECN and PFC 162

Why ECN Must Precede xOFF 163

DCQCN Configuration 166

References 174

Chapter 12: Flow, Flowlet, and Packet-Based Load Balancing 175

Introduction 175

RDMA WRITE Operation 176

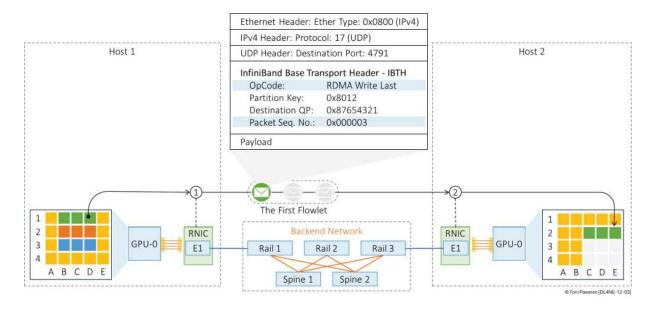

RDMA Write First 176

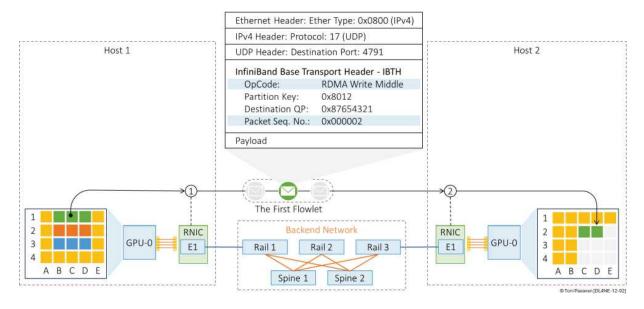

RDMA Write Middle 178

RDMA Write Last 179

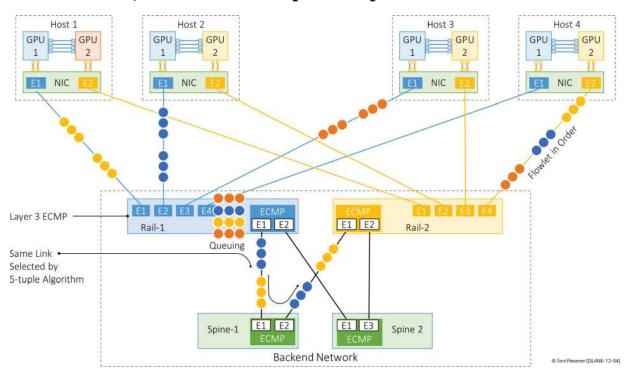

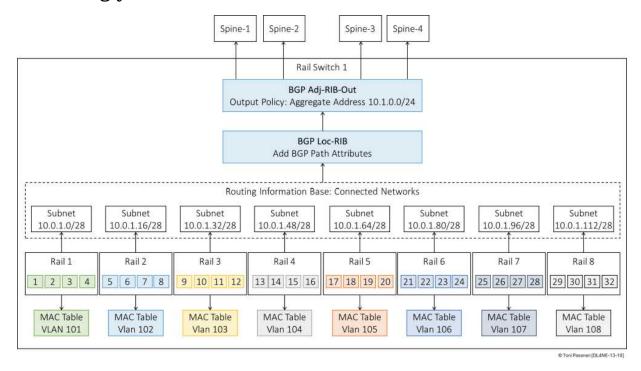

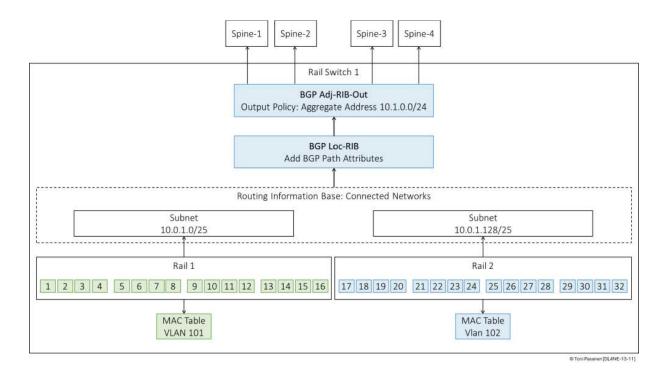

Flow-Based Load Balancing with Layer 3 ECMP 180

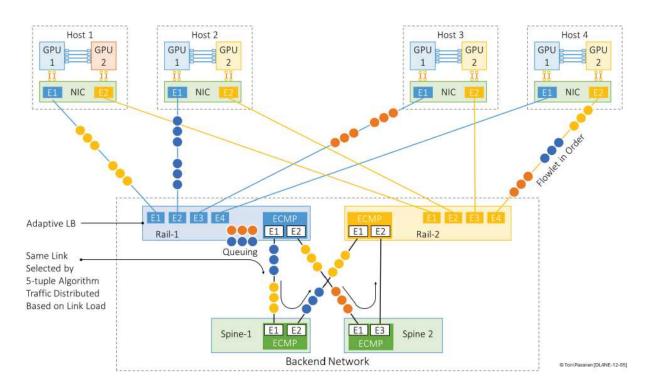

Flowlet-Based Load Balancing with Adaptive Routing 181

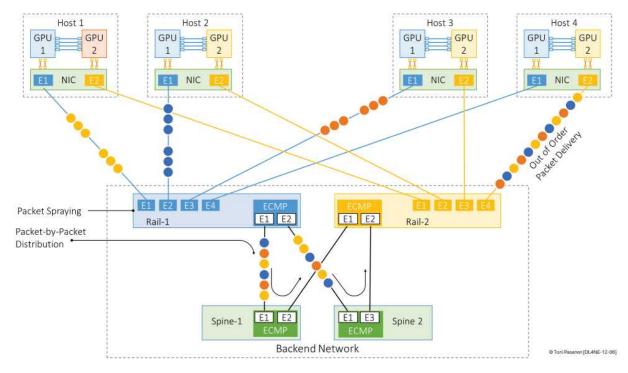

Packet-Based Load Balancing with Packet Spraying 183

RDMA Write Only 184

Configuring Per-Packet Load Balancing on Cisco Nexus Switches 185

References 186

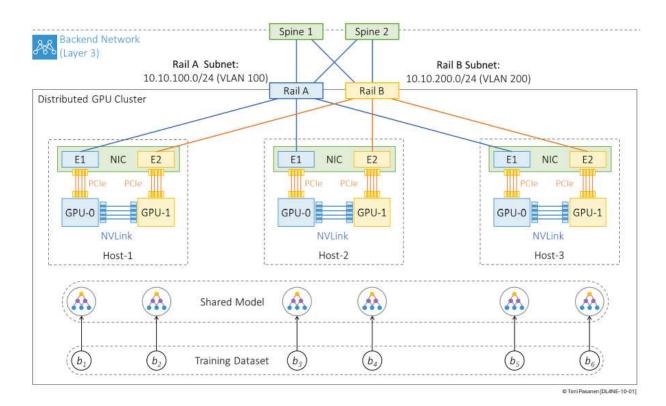

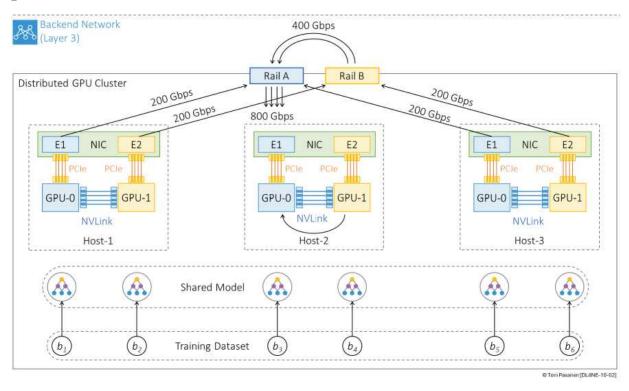

Chapter 13: Backend Network Topologies 187

Introduction 187

Shared NIC 187

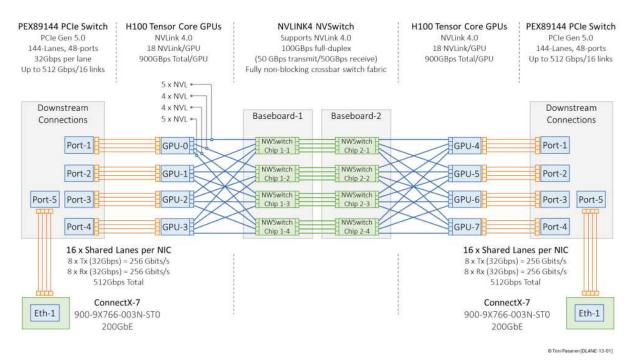

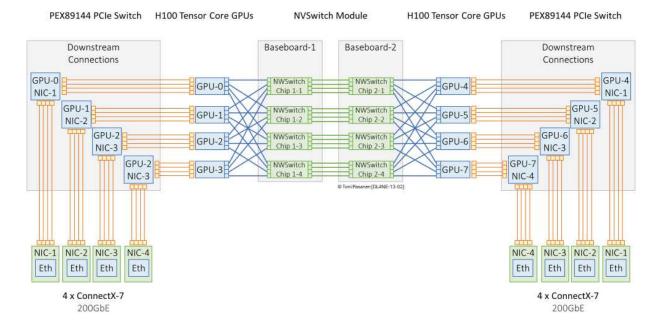

NIC per GPU 190

Design Scenarios 193

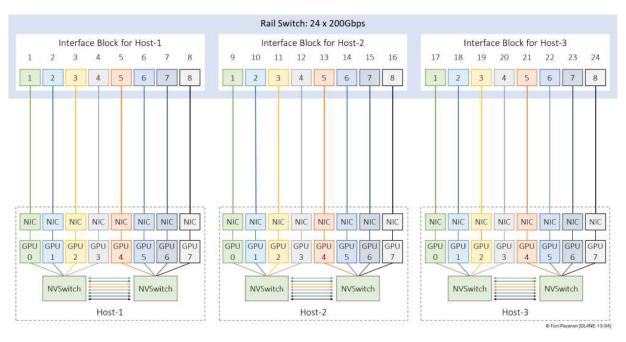

Single Rail Switch Design with Dedicated, Single-Port NICs per GPU 193

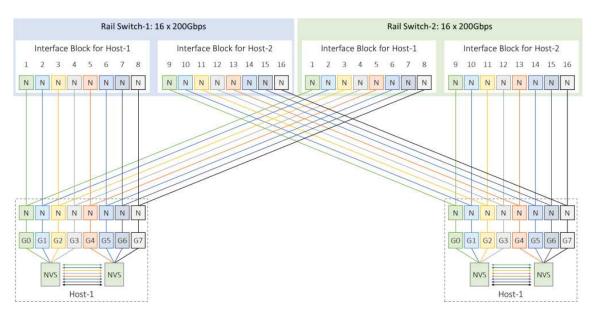

Dual-Rail Switch Topology with Dedicated, Dual-Port NICs per GPU 195

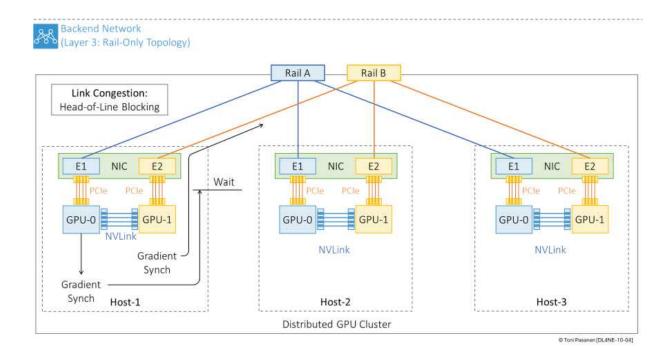

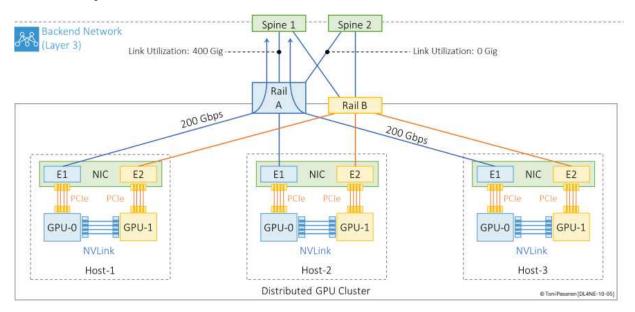

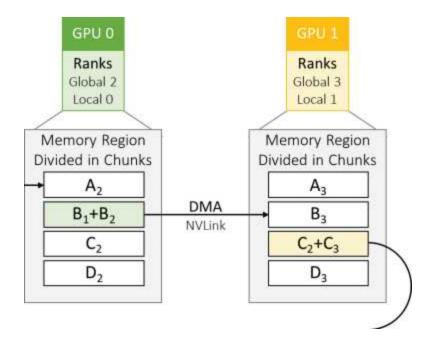

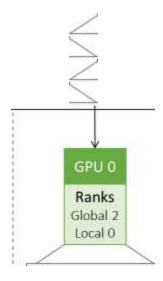

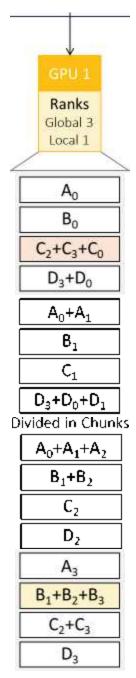

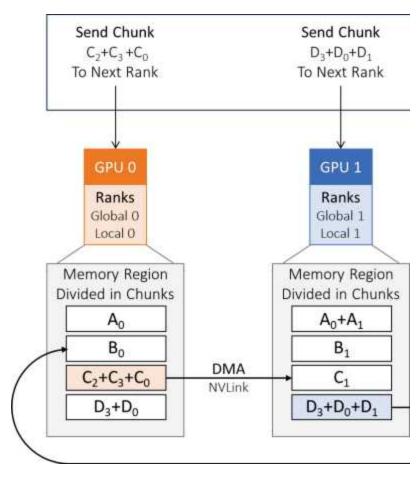

Cross-Rail Communication over NVLink in Rail-Only Topologies 199

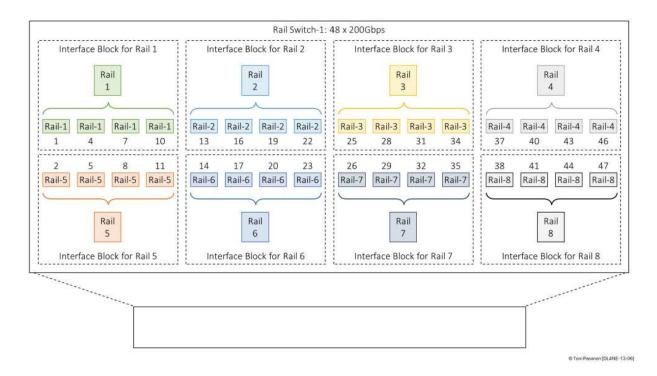

Rail Desings in GPU Fabric 205

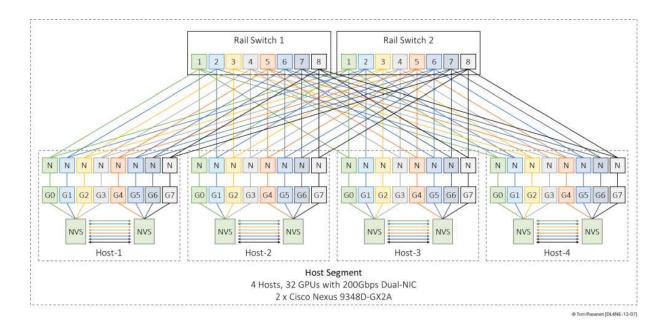

AI Fabric Architecture Conclusion 209

Hash Polarization 212

References 214

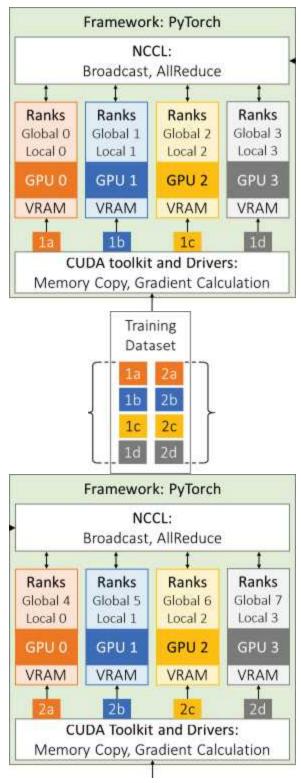

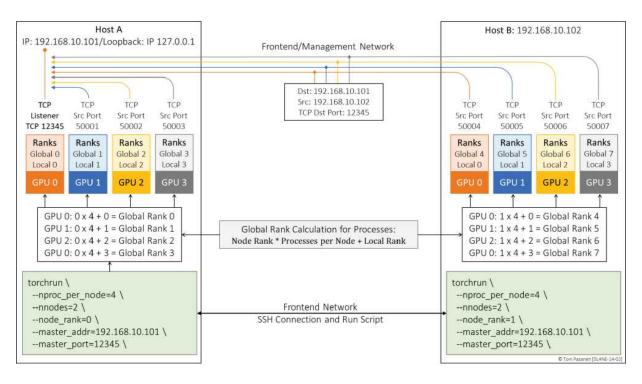

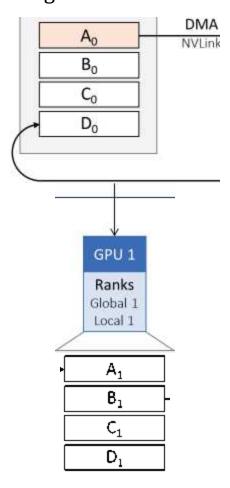

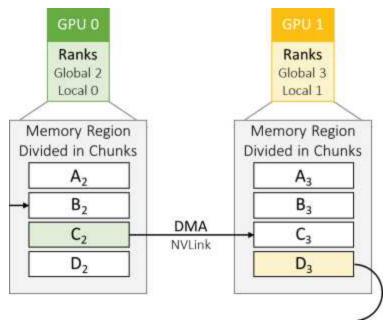

Chapter 14: GPU Cluster Communication Model 215

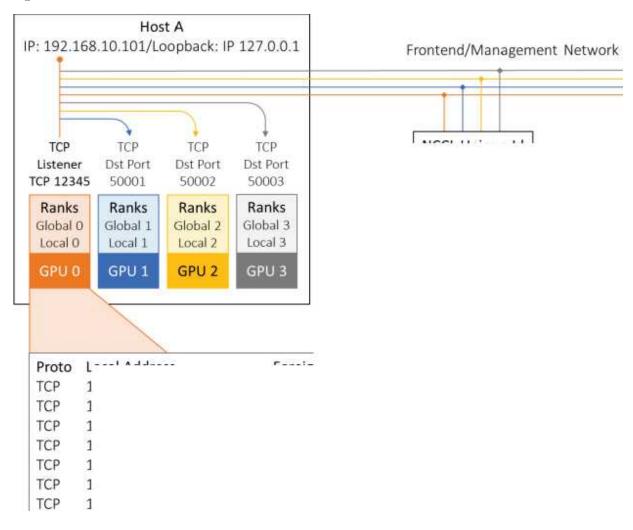

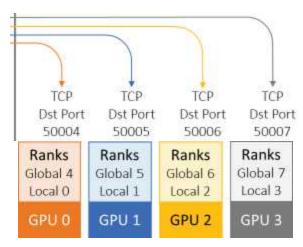

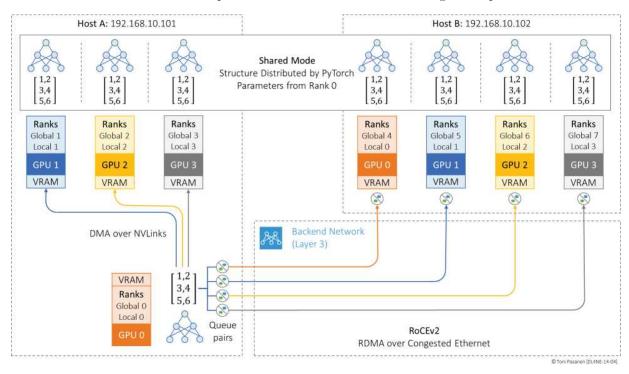

Distributing NCCL Unique Id for GPUs in a Training Cluster 217

Opening TCP Socket to Master Node 217

Distributing the NCCL Unique ID Over Established TCP Sockets 219

NCCL Broadcast Collective and Model Parameter Synchronization 220

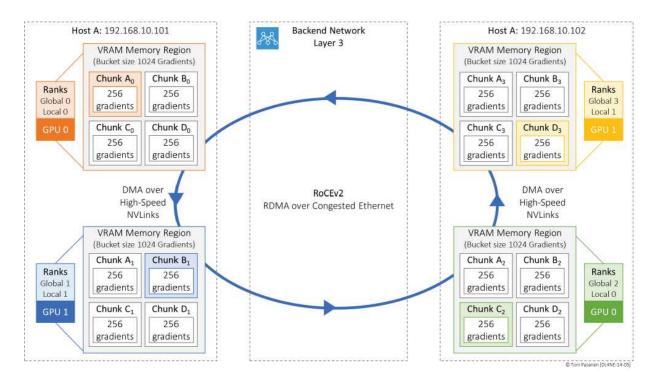

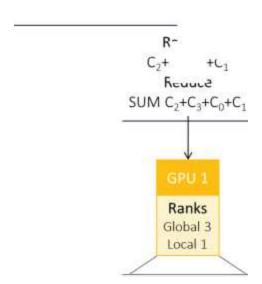

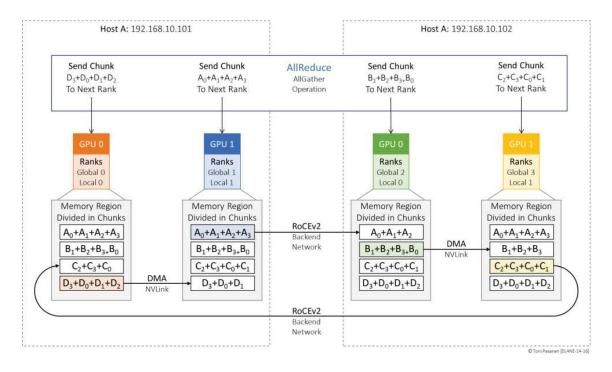

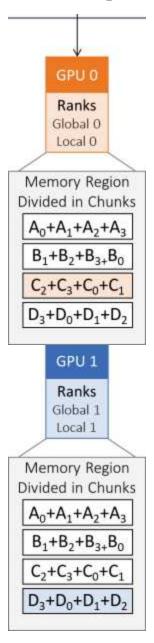

Gradient Synchronization Using AllReduce Collective 222

References 238

**Back Cover Text 240**

# CHAPTER 1: ARTIFICIAL NEURON

# INTRODUCTION

Before diving into the somewhat complex world of deep learning, let's first consider how humans learn new skills through repetition, feedback, and guidance.

Judo, as a martial art, serves as a good example. I trained in judo for over 20 years. During that time, I learned which throwing techniques to use to take down an opponent efficiently by leveraging their movement, energy, and reactions. But how did I learn that?

Through a supervised training process.

Our coach first taught us the throwing techniques and explained the situations in which they work best. We then practiced them, starting with static drills where the opponent stood still. Once the basic movement was learned, we moved on to pre-arranged sequences that introduced movement and timing.

Mastering these techniques required thousands of repetitions. Even then, perfect performance was not guaranteed, due to variables such as the opponent's movement, strength, body length, technical level, and so on.

After internalizing several throwing techniques, I reached a point where I could apply them in situations I hadn't

encountered before. That's when I was ready to compete, testing my skill in real matches, under the control of a referee who judged and scored the techniques.

How does this relate to Deep Learning?

Deep Learning (DL) is a driving force behind many of today's breakthroughs in artificial intelligence. It relies on Deep Neural Networks (DNNs)—systems made up of interconnected artificial neurons that learn

to recognize patterns in data. Deep Learning is a subfield of Machine Learning (ML), which enables computers to learn from data and make predictions or decisions without being explicitly programmed for every scenario. In turn, Machine Learning is part of the broader field of Artificial Intelligence (AI), which focuses on creating systems that can perform tasks that normally require human intelligence.

Training a neural network follows similar principles to learning a judo throwing technique.

In judo, my coach first taught me the correct technique: where to place my hands, how to shift my weight, and when to execute the throw. This is like supervised learning, where a neural network is trained with labeled data, input examples paired with the correct output, just like the coach provides correct demonstrations and feedback.

After I had practiced the technique in a static, controlled environment, we introduced more complexity by adding movement. I had to react to the opponent's motion and timing.

While the feedback was still there, the learning was now more intuitive and situational, similar to how a model can later benefit from unlabeled data or semi-supervised methods to generalize better.

Eventually, I entered competitions. There, I faced unpredictable situations, opponents with different styles, and no second chances. This is the equivalent of putting a trained neural network into production, where it must perform accurately on real-world data it hasn't seen before, without further coaching.

Like judo training, training a neural network takes time and repetition, often tens of thousands of iterations. After each iteration, the model's output is compared to the expected result, and its internal parameters are adjusted to reduce error. The process depends on several factors: dataset size, network architecture, hardware, and parallelization strategies. While training may take days or even months, the outcome is a system that can

respond quickly and reliably, just like a skilled judoka reacting instinctively in a match.

The duration of the training process depends on several factors, such as dataset size, network architecture, hardware, and selected parallelization strategies (if need). Training a neural network requires multiple iterations, sometimes even tens of thousands, where, at the end of each iteration, the model's output is compared to the actual value. If the difference between these two values is not small enough, the network is adjusted to improve performance. The entire process may take

months, but the result is a system that responds accurately and quickly, providing an excellent user experience.

This chapter begins by discussing the artificial neuron, and its functionality. We then move on to the Feedforward Neural Network (FFNN) model, first explaining its layered structure and how input data flows through it in a process called the Forward Pass (FP). Next, we examine how the FFNN is adjusted during the Backward Pass (BP), which fine-tunes the model by minimizing errors. The combination of FP and BP is known as the Backpropagation Algorithm.

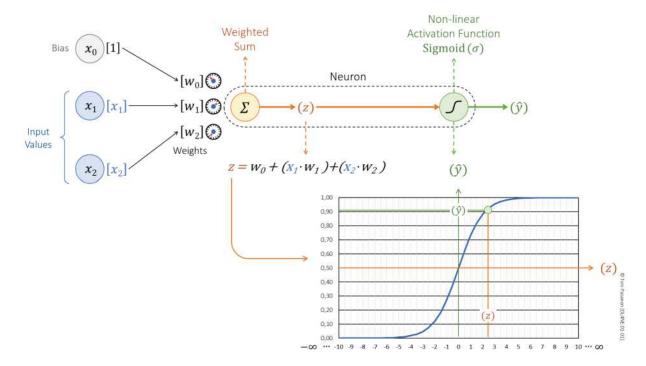

### ARTIFICIAL NEURON

An artificial neuron, also known as a perceptron, is a fundamental building block of any neural network. It functions as a computational unit that processes input data in two phases. First, it collects and processes all inputs (matrix multiplication), and then applies an activation function. Figure 1-1 illustrates the basic process without the complex mathematical functions (which I will explain later for those interested in studying them). On the left-hand side, we have a bias term and two input values, x1 and x2. The bias and inputs are connected to the perceptron through adjustable weight parameters: w0, w1, and w2, respectively. During the initial training phase, weight values are randomly generated.

## **Weighted Sum and Activation Function**

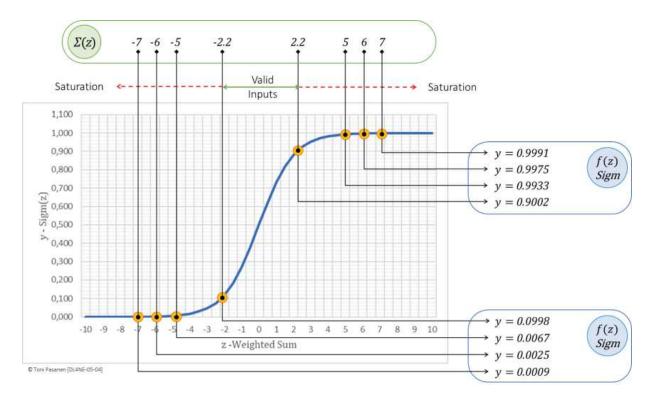

As the first step, the neuron calculates the weighted sum of inputs x1 and x2 and adds the bias. A weighted sum simply means that each input is multiplied by its corresponding weight parameter, the results are summed, and the bias is added to the total. The bias value is set to one, so its contribution is always equal to the value of its weight parameter. I will explain the purpose of the bias term later in this chapter. The result of the weighted sum is denoted as z, which serves as a pre-activation

value. This value is then passed through a non-linear activation function, which produces the actual output of the neuron,  $yy^{\wedge}$  (y-hat). Before explaining what non-linearity means in the context of activation functions and why it is used, consider the following: The input values fed into a neuron can be any number between negative infinity (- $\infty$ ) and positive infinity (+ $\infty$ ). Additionally, there may be thousands of input values. As a result, the weighted sum can become a very large positive or negative value.

Now, think about neural networks with thousands of neurons. In Feedforward Neural Networks (FFNNs), neurons are structured into layers: an input layer, one or more hidden layers, and an output layer. If input values were only processed through the weighted sum computation and passed to the next layer, the neuron outputs would grow linearly with each layer. Even if we applied a linear activation function, the same issue would persist—the output would continuously increase. With a vast number of neurons and large input values, this uncontrolled growth could lead to excessive computational demands, slowing down the training process. Non-linear activation functions help keep output values within a manageable range. For example, an S-shaped Sigmoid activation function squeezes the neuron's output to a range between 0 and 1, even for very large input values.

Let's go back to Figure 1-1, where we first multiply the input values by their respective weight parameters, sum them, and then add the bias. Since the bias value is 1, it is reasonable to

represent it using only its associated weight parameter in the formula. If we plot the result z on the horizontal

axis of a two-dimensional chart and draw a vertical line upwards, we obtain the neuron's output value y at the point where the line intersects the S-curve. Simple as that. Naturally, there is a mathematical definition and equation for this process, which is depicted in Figure 1-2.

Before moving on, there is one more thing to note. In the figure below, each weight has an associated adjustment knob. These knobs are simply a visual representation to indicate that weight values are adjustable parameters, which will be tuned by the backpropagation algorithm in case the model output is not close enough to expected result. The backpropagation process is covered in detail in a dedicated chapter.

Figure 1-1: An Architecture of an Artificial Neuron.

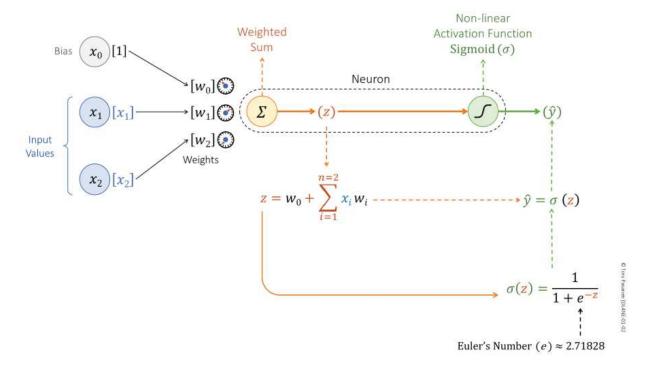

Figure 1-2 shows the mathematical equations for calculating the weighted sum and the Sigmoid function. The Greek letter used in the weighted sum equation is  $\Sigma$  (uppercase Sigma). The lowercase i is set to 1 beneath the Sigma symbol, indicating that the weighted sum calculation starts from the first pair of elements: input x1 and its corresponding weight w1. The notation n=2 specifies the total number of paired elements included in the weighted sum calculation. In our example, both input values and their respective weights are included.

After computing the weighted sum, we add the bias term. The result, z, is then passed through the Sigmoid function, producing the output  $yy^{\wedge}$ . The Sigmoid function is commonly represented by the Greek letter  $\sigma$  (lowercase sigma).

The lower equation in Figure 1-2 shows how the Sigmoid function is computed. To obtain the denominator for the fraction, Euler's number ( $e \approx 2.71828$ ) is raised to the power of -z and then summed with 1. The final output is simply the reciprocal of this sum.

Figure 1-2: The Math Behind an Artificial Neuron.

The formulas can be expressed in an even simpler manner using dot products, which are commonly used in linear algebra. Dot products frequently appear in research papers and deep learning literature.

In Figure 1-3, both input values and weights are arranged as column vectors. The notation for the input vector uses an uppercase X, while the weight vector is denoted by an uppercase W. Although these are technically vectors, it is not a major issue to illustrate them as a simple matrix for demonstration purposes. Generally speaking, a matrix has more than one row and column, as you will learn later.

The dot product performs a straightforward matrix multiplication, as shown in the figure. This greatly simplifies the computation.

Figure 1-3: Matrix Multiplication with Dot Product.

#### Bias term

Figures 1-4 and 1-5 illustrate how changes in the bias weight parameter affect the weighted sum and shift z horizontally. This, in turn, changes the output of the Sigmoid function and the neuron's final output.

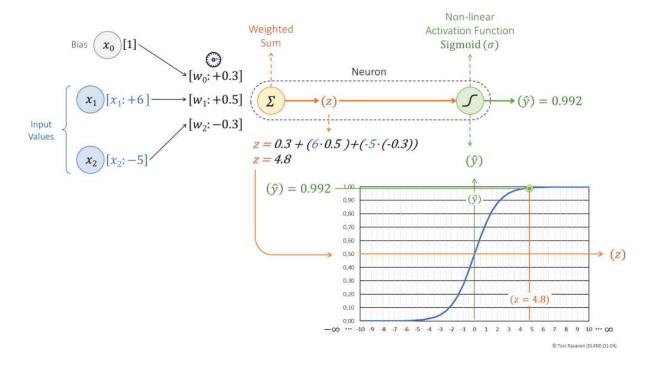

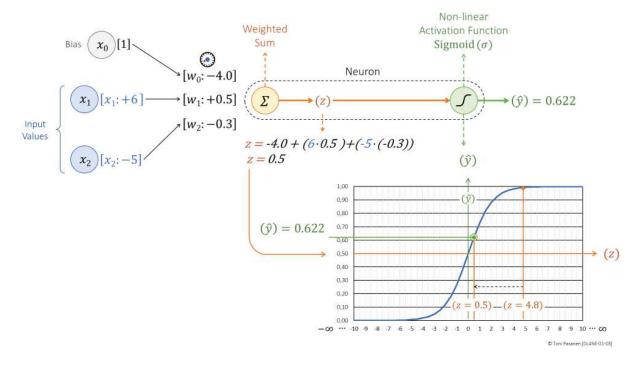

In Figure 1-4, the initial weight values for the bias, input x1, and input x2 are +0.3, +0.5, and -0.3, respectively. The calculated weighted sum is z=4.8. Applying the Sigmoid function to output z=4.8, we obtain an output value of 0.992. Figure 1-4 visualizes this process: z=4.8 is positioned on the horizontal axis, and the intersection with the S-curve results in an output of 0.992.

Figure 1-4: Construct of an Artificial Neuron.

Now, we adjust the weight wo associated with the bias from +0.3 down to -4.0. As a result, the weighted sum decreases from 4.84 to 0.50, shifting z 4.3 steps to the left on the horizontal axis. Applying the Sigmoid function to z, the neuron's output decreases from 0.992 to 0.622.

Figure 1-5: Construct of an Artificial Neuron.

In the example calculation above, imagine that input values x1 and x2 are zero. Without a bias term, the activation value will be zero, regardless of how large the weight parameters are. Therefore, the bias term also allows the neuron to produce non-zero outputs, even when all input values are

zero.

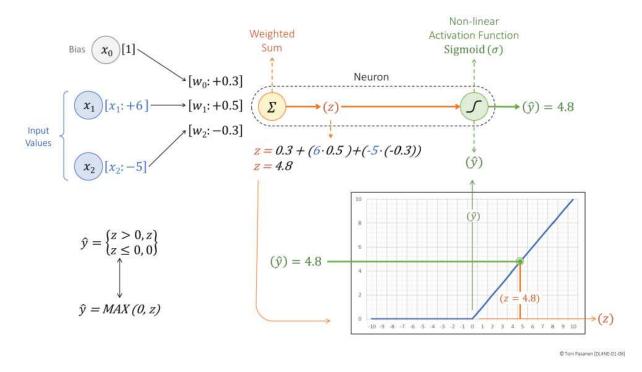

### **ReLU Activation Function**

A lighter alternative to the Sigmoid activation function is ReLU (Rectified Linear Unit). The ReLU activation function is non-linear for values less than or equal to zero and linear for values greater than zero. This means that if the weighted sum  $z \le 0$ , the output is zero. If z > 0, the output is equal to z.

From a computational perspective, ReLU requires fewer CPU cycles than the Sigmoid function. Figure 1-6 illustrates how z = 4.8 is processed by ReLU, resulting in an output value of  $yy^{} = 4.8$ . The figure also shows two common notations for ReLU. The first notation states:

- If z > 0, return z.

- If  $z \le 0$ , return 0.

The second notation, written as MAX(0,z), simply means selecting the greater value between 0 and z.

Figure 1-6: Artificial Neuron with a ReLU Activation Function.

#### **NETWORK IMPACT**

A single artificial neuron is the smallest unit of a neural network. The size of the neuron depends on its connections to input nodes. Every connection has an associated weight parameter, which is typically a 32-bit value. In our example, with 2 connections and bias, the size of the neuron is  $3 \times 32$  bits = 96 bits.

Although we haven't defined the size of the input in this example, let's assume that each input (x) is an 8-bit value, giving us  $2 \times 8$  bits = 16 bits for the input data. Thus, our single neuron "model" requires 96 bits for the weights plus 16 bits for the input data, totaling 112 bits of memory. This is small enough to not require parallelization. Besides, the weight parameters and input values, the result of weighted sum and the neuron output must be stored for processing.

However, if the memory requirement of the neural network model combined with the input data exceeds the memory capacity of a GPU, a parallelization strategy is needed. The data can be split across multiple GPUs within a single server, with synchronization happening over highspeed NVLink. If the job must be divided between multiple GPU servers, synchronization occurs over the backend network, which must provide lossless, high-speed packet forwarding.

Parallelization strategies will be discussed in the next chapter, which introduces a Feedforward Neural Network using the Backpropagation algorithm, and in later chapters dedicated to Parallelization (Chapter 8).

#### **SUMMARY**

Deep Learning leverages Neural Networks, which consist of artificial neurons. An artificial neuron mimics the structure and operation of a biological neuron. Input data is fed to the neuron through connections, each with its own weight parameter. The neuron uses these weights to calculate a weighted sum of the inputs, known as the pre-activation value. This result is then passed through an activation function, which provides the post-activation value, or the actual output of the neuron. The activation functions discussed in this chapter are the non-linear ReLU (Rectified Linear Unit) and logistic Sigmoid functions.

#### REFERENCES

- [1] Magnus Ekman, "Learning Deep Learning: Theory and Practice of Neural Networks, Computer Vision, Natural Language Processing, and Transformers Using TensorFlow", 17 Aug. 2021

- [2] Yann LeCun, Corina Cortes, Christoper J.C. Burges: The MNIST database of handwritten digits.

### https://www.lri.fr/~marc/Master2/MNIST\_doc.pdf

[3] Alex Krizhevsky, Vinod Nair, and Geoffrey Hinton: The CIFAR-10 dataset.

#### https://www.cs.toronto.edu/~kriz/cifar.html

[4] Alex Krizhevsky, Learning Multiple Layers of Features from Tiny Images, April 2009

<u>https://www.cs.toronto.edu/~kriz/learning-features-2009-TR.pdf</u>

[5] Jason Brownlee: A Gentle Introduction to the Rectified Linear Unit (ReLU), August 20, 2020.

<u>https://machinelearningmastery.com/rectified-linear-activation-function-for-deep-learning-neural-networks/</u>

[6] Eric W. Weisstein: Wolfram Mathworld – Hyperbolic Tangent

https://mathworld.wolfram.com/HyperbolicTangent.html

[7] Eric W. Weisstein: Wolfram Mathworld – Sigmoid Tangent

https://mathworld.wolfram.com/SigmoidFunction.html

14 Chapter 1: Artificial Neuron

# CHAPTER 2: BACKPROPAGATION ALGORITHM

### INTRODUCTION

The previous chapter explained the operation of a single artificial neuron. It covered how input values are multiplied by their respective weight parameters, summed together, and combined with a bias term. The resulting value, z, is then passed through a non-linear sigmoid function, which squeezed a neuron's output value  $yy^{\wedge}$  between 0 and 1.

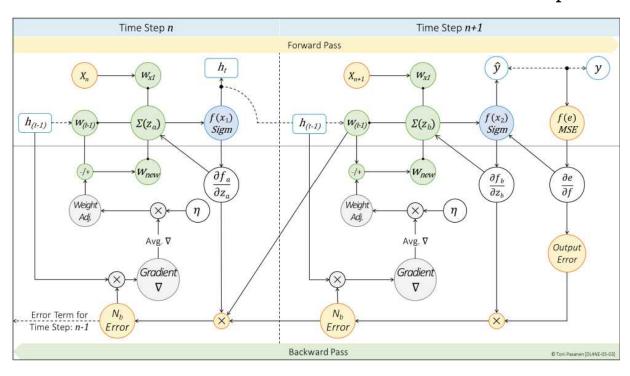

In this chapter, we form the smallest possible Feed Forward Neural Network (FFNN) model using only two neurons. While this is far from a Deep Neural Network (DNN), a simple NN with two neurons is sufficient to explain the Backpropagation algorithm, which is the focus of this chapter.

The goal is to demonstrate the training process and illustrate how the Forward Pass (computation phase) first generates a model output,  $yy^{\wedge}$ . The algorithm then evaluates the model's accuracy by computing the error term using Mean Squared Error (MSE). The first training iteration rarely, if ever, produces a perfect output. To gradually bring the training result closer to the expected value, the Backward Pass (adjustment and communication phase) calculates the magnitude and direction by which the weight values should be adjusted. We are using a supervised training process with a prelabeled test dataset, although it is not shown in Figure 2-1. Chapter Three covers the training datasets in detail.

After the training process is completed, we use a test dataset to evaluate the model's performance. Test dataset also contains input data and labels, but these labels are not used during training. Instead, after training is complete, the model is evaluated on the test dataset to measure its performance. At this phase, we measure how well the predictions from the training and test phases align. When the model produces the expected results on the test dataset, it can be taken into production.

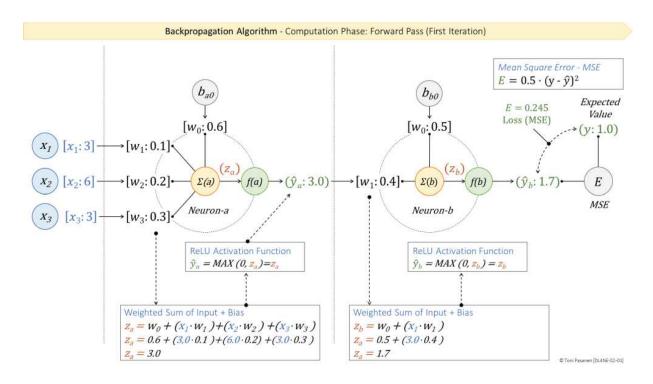

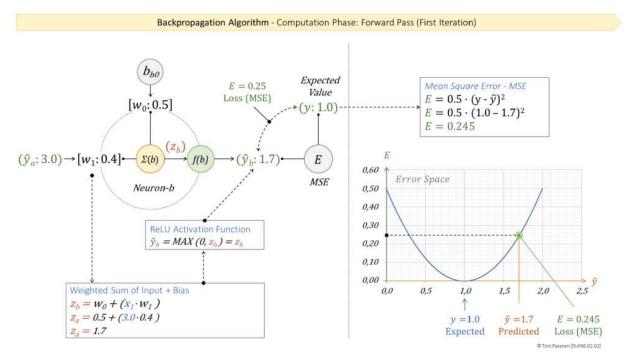

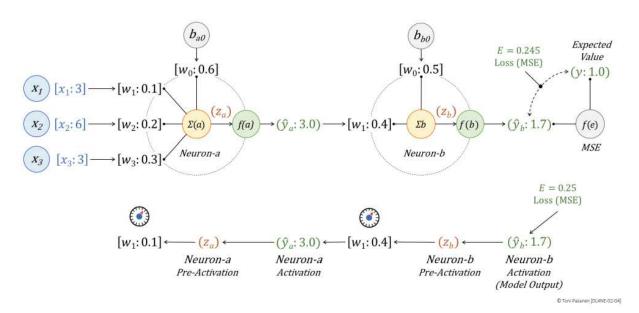

### FORWARD PASS

Figure 2-1 illustrates how neuron-a computes a weighted sum from three input values, adds a bias term, and produces a preactivation value za. This value is then passed through the Sigmoid activation function. The output yy^a from neuron-a serves as an input for neuron-b, which processes it and generates the final model output yy^b. Since these computational steps were covered in detail in Chapter 1, we will not repeat them here.

As the final step of the Forward Pass, we apply the error function E to the model output. The error function measures how far model output  $yy^b$  is from expected value y. We use the Mean Squared Error (MSE), which is computed by subtracting the expected value from the model's output, squaring the result, and multiplying it by 0.5 (or equivalently, dividing by two).

Figure 2-1: An Overview of a Complete Forward Pass Process.

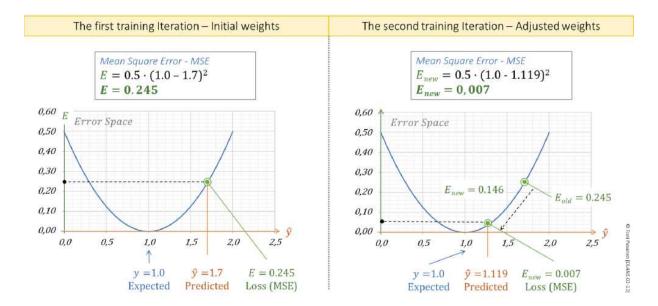

On the right side of Figure 2-2, we have a two-dimensional error space. In this space, a symmetric parabolic curve visualizes the error function. The curve is centered at the expected value, which is 1.0 in our example. The horizontal axis represents the model output,  $yy^{\wedge}$ , and the vertical axis represents the error E. For instance, if the model prediction is 1.7, you can draw a vertical line from this point on the horizontal axis to meet the parabolic curve. In our case, this intersection shows an error term of 0.245. In real-life scenarios, the error landscape often has many peaks and valleys rather than a simple symmetric curve.

The Mean Squared Error (MSE) is a loss function that measures the difference between the predicted values and the expected values. It provides an overall error value for the model, which is also called the loss or cost, indicates how far off the predictions are.

Next, the gradient is computed by taking the derivative of the loss function with respect to the model's weights. This gradient shows both the direction and the magnitude of the steepest increase in error. During the Backward Pass, the algorithm calculates the gradient for each weight. By moving in the opposite direction of the gradient (using a method called Gradient Descent), the algorithm adjusts the weights to reduce the loss. This process is repeated many times so that the model output gradually becomes closer to the expected value. The Backward pass process is explained right after the Learning Rate section.

The following sections will cover the processes and computations performed during the Backward Pass.

Figure 2-2: Mean Square Error.

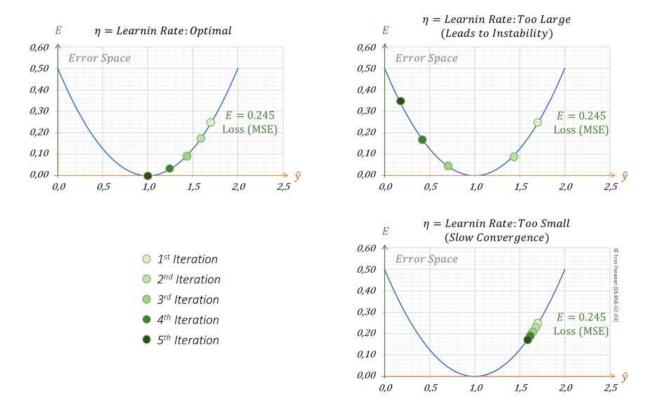

#### LEARNING RATE

Besides determining the direction in which the error should be reduced, the process also needs to know the size of each adjustment step. This is defined by the Learning Rate. The Learning Rate value affects how much the weights are adjusted in response to the gradient during each iteration of the Backward Pass. A small Learning Rate leads to small, gradual changes, which may result in slower training but a more stable convergence. On the other hand, a large Learning Rate can speed up training by making larger adjustments, yet it might overshoot the optimal values and cause instability. Therefore, choosing the right Learning Rate is crucial for effective and efficient training. This is illustrated in the Figure 23. We will get back to Learning Rate in the Backward Pass section.

Figure 2-3: Learning Rate.

#### **BACKWARD PASS**

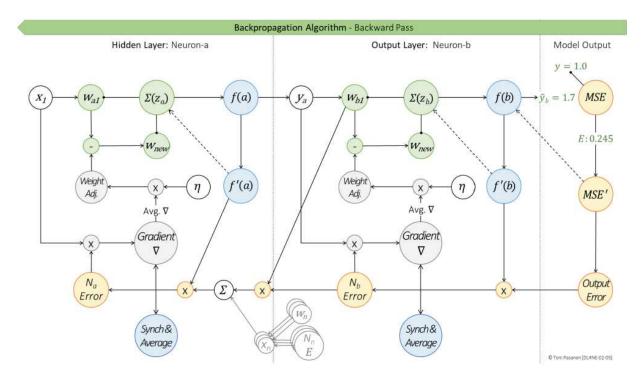

The Forward Pass produces the model output  $\hat{y}$ , which is then used to compute the model error E. The closer  $\hat{y}$  is to the expected value y, the smaller the error, indicating better model performance. The purpose of the Backward Pass, as part of the Backpropagation algorithm, is to adjust the model's weight parameters during training in a direction that gradually moves the model's predictions closer to the expected values y.

In Figure 2-4, the model's output ŷb depends on the weighted sum zb of neuron-b. This weighted sum zb, in turn, is calculated by multiplying an input value ya by its associated weights w1. The same process applies to neuron-a. Backpropagation algorithm cannot directly modify the results of an activation function or the weighted sum itself. Nor can it alter the input values directly. Instead, it calculates weight adjustments, which are then used to update the model's weights.

Figure 2-4 illustrates this dependency chain and provides a high-level overview of how the Backpropagation algorithm determines weight adjustments. The following sections will explain this process in detail.

**Figure 2-4:** Backpropagation Overview: Backward Pass Dependency Chain.

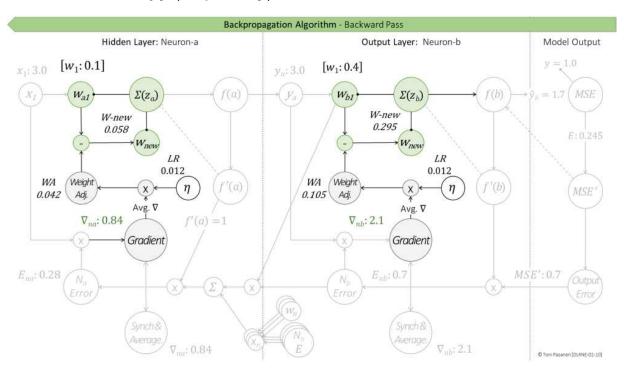

The somewhat crowded Figure 2-5 illustrates the components of the backpropagation algorithm, along with their relationships and dependencies. The figure consists of three main blocks. The rightmost block depicts the calculation of the error function. The middle and left blocks outline the steps for defining and adjusting new weight values. The complete backward pass process is explained next in detail, one step at a time.

Figure 2-5: The Backward Pass Overview.

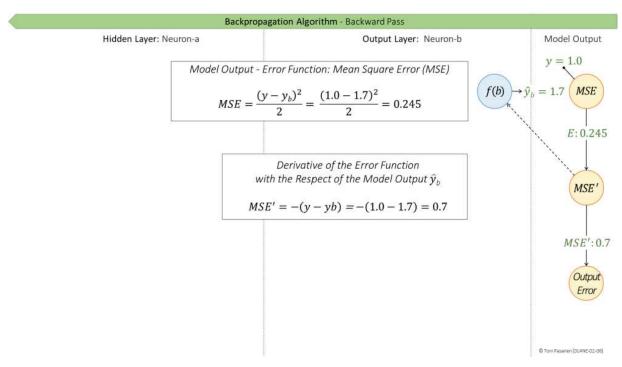

# Partial Derivative for Error Function – Output Error

The goal of training a model is to minimize the error, meaning we want  $yy^b$  (the model's prediction/output) to get as close as possible to y (the expected value).

After computing the error E (=0.245), we compute the partial derivative of the error function with respect to yb (=1.7), which shows how small changes in  $yy^b$  affects the error E. A derivative is called partial when one of its input values is held constant (i.e., not adjusted by the algorithm). In our example, the expected value y is constant input. The result of the partial derivative of the error function indicates how the predicted output  $yy^b$  should change to minimize the model's error.

We use the following formula for computing the derivative of the error function:

Since the model output yb = 1.7 is too high, the positive gradient suggests that it should be lowered by 0.7, which is the derivative of the error function (MSE'). This makes perfect sense because by subtracting the MSE's 0.7 from the model output yb = 1.7, we obtain 1.0, which matches the expected value.

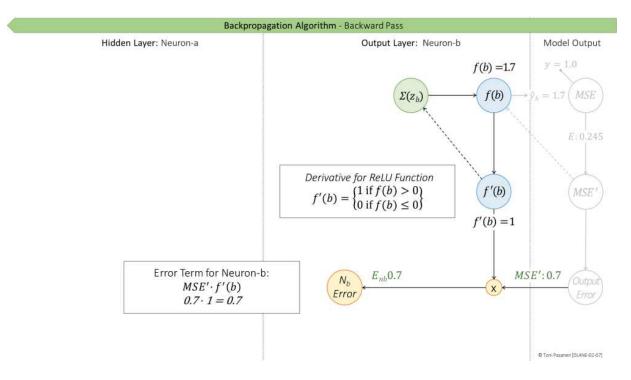

### Partial Derivative for the Activation Function

After computing the output error, we calculate the derivative of the activation function f(b) with respect to zb. Neuron-b uses a ReLU activation function, which states that if the function's output is greater than 0, the derivative is 1; otherwise, it is 0. In our case, the result of the activation function f(b)=1.7, so the derivative is 1.

$$ff'(yy) = ^$$

1, if  $ff(yy) > 0$

0, if  $ff(yy) \le 0$

#### **Error Term for Neurons**

The error term for neuron-b is calculated by multiplying the partial derivative of the error function MSE' = 0.7, by the derivative of the neuron's activation function ff'(yy)= 1.0. This means we propagate the model's error backward using it as a base value for finetuning the model accuracy (i.e., refining new weight values). This is why the term backward pass fits perfectly for the process.

Error term (Enb) for Neuron-b = MSE'  $\cdot ff'(yy) = 0.7 \cdot 1 = 0.7$

Figure 2-7: The Backward Pass – Error Term for Neuron-b.

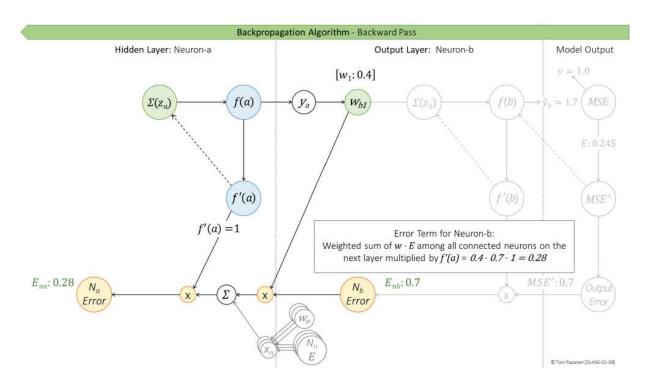

After computing the error term for neuron-b, the backward pass moves to the preceding layer, the hidden layer, to calculate the error term for neuron a. First, the process computes a weighted sum of  $w \cdot E$  across all connected neurons in the next layer, output layer in our example. This sum is then multiplied by the derivative of the activation function, ff'(a). Since neurona is only connected to neuron-b, its error term is calculated as  $w1 \cdot Enb \cdot ff'(a)$ , resulting error term for neuron-a,  $Ean = 0.4 \cdot 0.7 \cdot 1 = 0.28$ .

Figure 2-8: The Backward Pass – Error Term for Neuron-a.

### **Gradient Calculation**

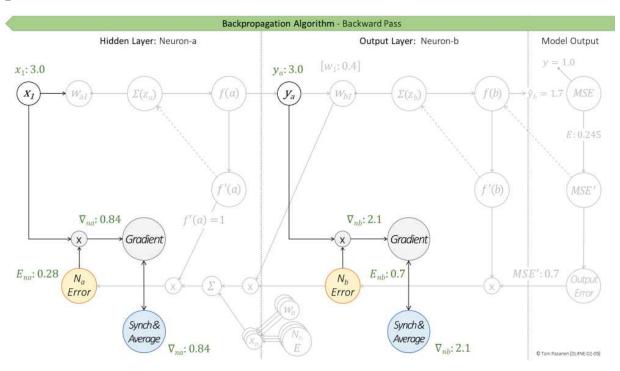

After computing the error terms for all neurons in every layer, the algorithm simultaneously calculates gradients for all weight parameters. Each gradient is determined by multiplying the input value by the corresponding error term.

In our example, the gradient for weight wa1, which connects input x1 to neuron-a, is calculated by multiplying the input value x1 (=3.0) by the error term Ena of neuron-a (= 0.28), resulting in a gradient of 0.84. Similarly, the gradient for weight wb1 in neuron-b is computed by multiplying the output y (=3.0) of the activation function from neuron-a by the error term Enb of neuron b (=0.7), yielding a gradient of 2.1.

If the test dataset is divided across multiple GPUs, gradients must be synchronized before computing the actual weight-based adjustment values. Each GPU sums all received gradients, including its own. The sum is then averaged by dividing it by the number of GPUs. This process is explained in detail in Chapter 8. Next, the GPUs synchronize these averaged gradients to ensure that each one uses the same values when calculating the final weight adjustments. This process is part of a data parallelization strategy, where the training dataset is too large to fit into a single GPU's memory and is split into micro-batches. Each GPU processes its micro-batches using the same model with the same parameters.

**Figure 2-9:** The Backward Pass – Gradient for Neurons.

# Weight Adjustment

The weight adjustment value is computed by multiplying the gradient, averaged in our example, by the learning rate  $\eta$ . We use a learning rate of 0.012. This results in a weight adjustment of 0.042 for weight wal and 0.105 for weight wb1.

The weight adjustment values are then subtracted from the initial weights. This yields an updated weight of 0.058 (0.1-0.042) for wal and 0.295 (0.4-0.105) for wbl.

Figure 2-10: The Backward Pass – Compute New Weight Values.

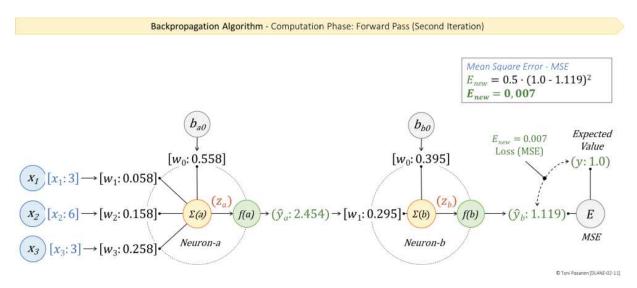

### THE SECOND ITERATION - FORWARD PASS

After updating all the weight values, including those associated with biases, the backpropagation process begins the second iteration of the forward pass. As shown in Figure 2-11, the model output  $yy^b = 1.28$  is very

close to the expected value y = 1.0. The new MSE = 0.007 is significantly lower than the initial MSE = 0.245 computed in the first iteration.

Figure 2-11: The Second Iteration of the Forward Pass.

In Figure 2-12, we have two 2-dimensional error spaces. Using the initial weight values, the model output is 1.7, resulting in an MSE of 0.245. After adjusting the weights, the model prediction is 1.119, reducing the MSE to 0.007.

Figure 2-12: Results Comparison.

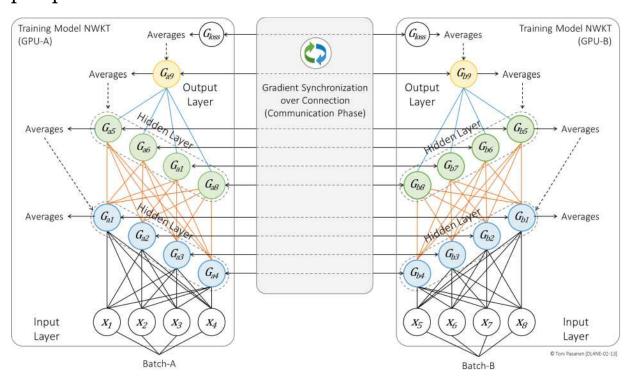

#### **NETWORK IMPACT**

In figure 2-13 we have a fully-connected Feed Forward Neural Network (FFNN) with four layers; input layer, two hidden layers, and output layer. Training data set is split into two batches, A and B, which are processed by GPU-A and GPU-B.

After computing a model prediction during the forward pass, the backpropagation algorithm begins the backward pass by calculating the gradient (output error) for the error function. Once computed, the gradients are synchronized between the GPUs. The algorithm then averages the gradients, and the process moves to the preceding layer. Neurons in the preceding layer calculate their gradient by multiplying the weighted sum of their connected neurons' averaged gradients and connected weight with the local activation function's partial derivative. These neuron-based gradients are then synchronized over connections (the process is explained in detail in chapter 14). Before the process moves to the preceding layer, gradients are averaged. The backpropagation algorithm executes the same process through all layers.

If packet loss occurs during the synchronization, it can ruin the entire training process, which would need to be restarted unless snapshots were taken. The cost of losing even a single packet could be enormous, especially if training has been ongoing for several days or weeks. Why is a single packet so important? If the synchronization between the gradients of two parallel neurons fails due to packet loss, the algorithm cannot compute the average, and the neurons in the preceding layer cannot calculate their gradient. Besides, if the connection, whether the synchronization happens over NVLink, InfiniBand, Ethernet (RoCE or RoCEv2), or wireless connection, causes a delay, the completeness of the training slows down. This causes GPU under-utilization which is not efficient from the business perspective.

**Figure 2-13:** Backward Pass – Gradient Synchronization and Averaging.

### **REFERENCES**

- [1] Magnus Ekman, "Learning Deep Learning: Theory and Practice of Neural Networks, Computer Vision, Natural Language Processing, and Transformers Using TensorFlow", 17 Aug. 2021

- [2] Goodfellow, I., Bengio, Y., & Courville, A. (2016, November 18). Deep Learning. MIT Press.

## https://www.deeplearningbook.org/

[3] Nielsen, M. (2015). Neural Networks and Deep Learning – Chapter 2: How the Backpropagation Algorithm Works. Determination Press.

### http://neuralnetworksanddeeplearning.com/chap2.html

[4] LeCun, Y., Bottou, L., Orr, G. B., & Müller, K. R. (2012). Efficient BackProp. In Neural Networks: Tricks of the Trade (pp. 9–50). Springer.

#### https://yann.lecun.com/exdb/publis/pdf/lecun-98b.pdf

[5] Stanford University (CS231n). (2025, April 10). Lecture 4: Neural Networks and Backpropagation.

https://cs231n.stanford.edu/slides/2025/lecture 4.pdf

[6] MIT Vision Book. (2024, April 16). Chapter 14 – Backpropagation. In Foundations of Computer Vision. MIT Press.

https://visionbook.mit.edu/backpropagation.html

[7] Mazur, M. (2015, March 17). A Step by Step Backpropagation Example.

<u>https://mattmazur.com/2015/03/17/a-step-by-step-backpropagation-example/</u>

# CHAPTER 3: MULTI-CLASS CLASSIFICATION

## **INTRODUCTION**

This chapter explains the multi-class classification training process. It begins with an introduction to the MNIST dataset (Modified National Institute of Standards and Technology). Next, it describes how the SoftMax activation function computes the probability distribution over digit classes during the forward pass and how the model's weight parameters are updated during the backward pass to improve classification accuracy. Additionally, the chapter discusses the data parallelization strategy from a network perspective.

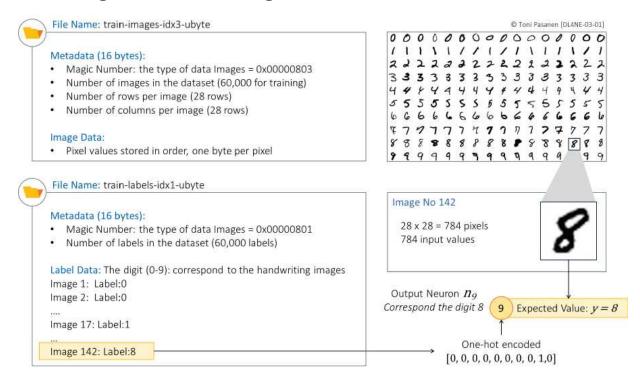

## **MNIST DATASET**

We will use the MNIST dataset, which consists of grayscale images of handwritten digits, to demonstrate the training process. The MNIST dataset includes four binary files: a training set with 60,000 images and their corresponding labels, and a test set with 10,000 images and labels. Each image is 28×28 pixels in size.

#### The files are:

train-images-idx3-ubyte: contains the pixel values for the training images, along with metadata describing the file format.

train-labels-idx1-ubyte: contains the labels (digits o-9)

corresponding to each image in the training set.

t10k-images-idx3-ubyte: contains the test images.

t10k-labels-idx1-ubyte: contains the labels for the test images.

Since there are ten possible digits (0–9), the output layer of the model uses ten neurons, each representing one digit class.

Before training begins, the labels for each image-label pair are one-hot encoded. This means that each label is transformed into a vector of ten elements: the correct class is represented by a 1 at its index position, and all other positions are set to 0. For example, if an image corresponds to the digit 8, the one-hot

vector would be [0, 0, 0, 0, 0, 0, 0, 0, 1, 0] (index 8 is set to 1, assuming 0-based indexing).

Figure 3-1: Training Dataset & Labels – The MNIST Database.

### **FORWARD PASS**

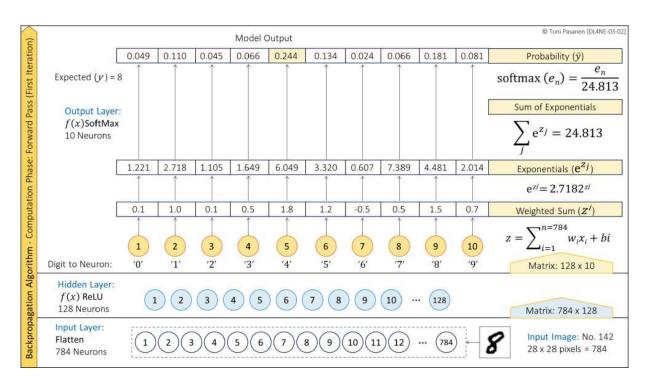

# **Model Probability**

Figures 3-2 and 3-3 illustrate the forward pass process for multiclass classification. The Input Layer flattens the 28 x28 pixel image into 784 input parameters, where each parameter represents the intensity of a pixel (0 = black, 255 = white). These 784 input values are then passed to all 128 neurons in the Hidden Layer. Each neuron in the hidden layer receives all 784 inputs, and each of these inputs is associated with a unique weight. Therefore, each of 128 neurons have 784 weight parameters, and total weight parameter count of hidden layer is 100 352.

In the hidden layer, each neuron computes the weighted sum (

= Matrix Multiplication) of its inputs and then applies the ReLU

activation function to the result. This process produces 128

activation values, one for each neuron in the hidden layer.

Next, these 128 activation values are fed into the Output Layer, which consists of 10 neurons (corresponding to the 10 possible classes for the MNIST dataset). Each output neuron is connected to all 128 activation values from the hidden layer. Therefore, the weight parameter counts in the output layer is 1280. Again, each neuron does matrix multiplication by computing a weighted sum of its inputs. The result of this calculation is called a logit.

In the output layer, the SoftMax activation function is applied to these logits. SoftMax first computes the exponential of each logit, using Euler's number e as the base. Then, it computes the sum of these exponentials, which in this example is 24.813. The probability for each class (denoted as  $yy^{\wedge}$ ) is calculated by dividing each neuron's exponential by the sum of all exponentials.

In this example, the output neuron corresponding to class "5" produces the highest probability, meaning the model predicts the digit in the image is 5. However, since this prediction is incorrect in the first iteration, the model will adjust its weights during backpropagation.

In our model, we have 101,632 weight parameters. The number of bits used to store each weight parameter in a neural network depends on the numerical precision chosen for the model. The 32-bit floating point (FP32 – single precision) is the standard precision used, where each weight is represented using 32 bits (4 bytes). This format offers good precision but can be memoryintensive for large models. To reduce memory usage and increase speed, many modern hardware systems use 16-bit floating point (FP16 – half precision), where each weight is represented using 16 bits (2 bytes). There is also 64-bit floating point (FP64 – double precision), which uses 64 bits (8 bytes), providing more precision and a larger range than FP32, but at the cost of increased memory usage.

In our model, using FP32, the memory required for the weight parameters is 406,528 bytes  $(4 \times 101,632)$ .

Figure 3-2: Forward pass – Probability Computation.

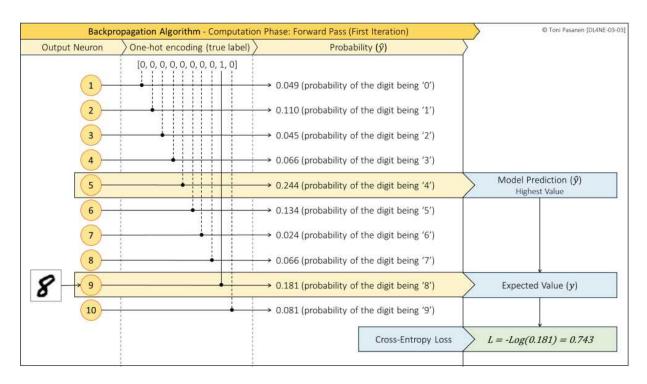

# **Cross-Entropy Loss**

In our example, the highest probability value (0.244) is provided by neuron 5, though the expected value should be produced by neuron 9. Next, the algorithm computes the cross-entropy loss by taking the logarithm of the probability value for the expected neuron, as defined by the one-hot encoded label. In our example, the probability of the digit being 8, computed by neuron 9, is 0.181. The cross-entropy loss is calculated by taking the log of 0.181, resulting in 0.734.

Figure 3-3: Forward pass – Cross-Entropy Loss.

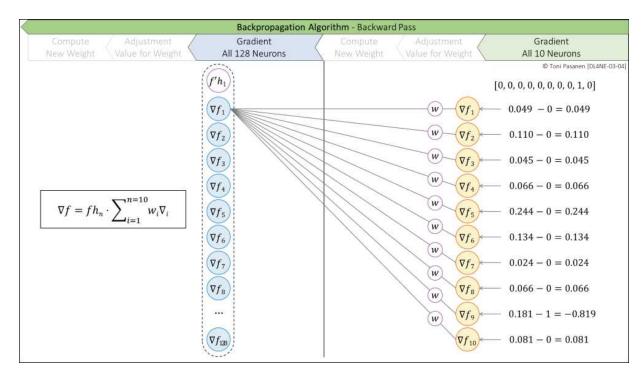

### BACKWARD PASS

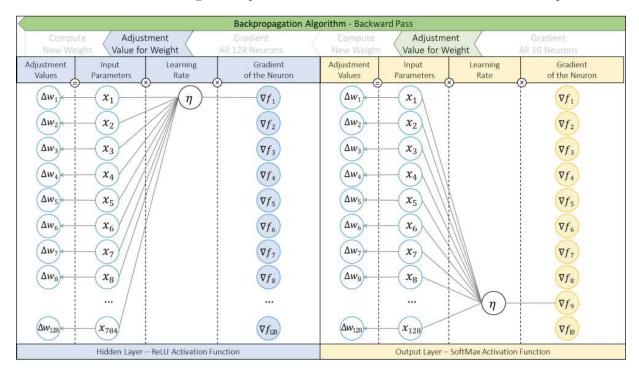

# **Gradient Computing**

The gradient for the neurons in the output layer is calculated by subtracting the ground truth values (from the one-hot encoded label) from the probabilities produced by the SoftMax function. This simplified gradient expression is a result of combining the SoftMax activation with the crossentropy loss, which cancels out more complex derivative terms. While the cross-entropy loss influences the training process, its derivative is implicitly included in this simplified gradient expression.

For neurons in the hidden layer, the gradient is computed by taking the weighted sum of the gradients from the connected output neurons. This sum is then multiplied by the derivative of the hidden neuron's activation function (such as ReLU). The formula for this computation is shown in Figure 3-4.

Figure 3-4: Backward pass - Gradient Calculation.

# Weight Adjustment Values

After calculating the gradients for all neurons, the backpropagation algorithm determines the weight adjustments. While this process was explained in the previous chapter, let's briefly recap it here. Each weight adjustment is computed by multiplying the gradient of the neuron it connects to (the downstream neuron) by the input that passed through that weight during the forward pass. This product represents the gradient of the weight. The actual adjustment is then calculated by multiplying this gradient by the learning rate — a shared hyperparameter that controls how much the weight is updated during training.

Figure 3-5 illustrates the computation from two perspectives: neuron 9 in the output layer and neuron 1 in the hidden layer.

Figure 3-5: Backward Pass - Weight Adjustment Value.

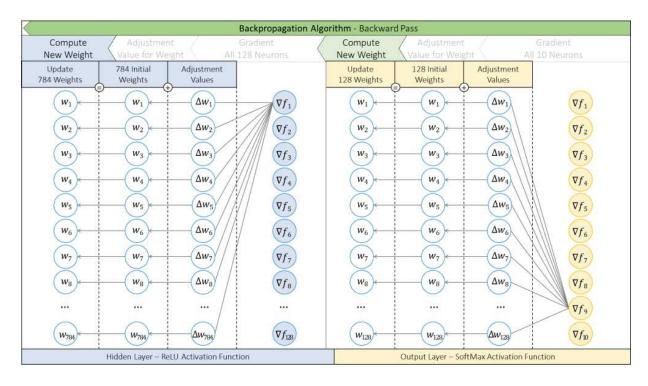

# Weight Update

Figure 3-6 depicts how the new weight value is obtained by adding the adjustment value to the initial weight value.

**Figure 3-6:** Backward Pass – Computing New Value for the Weight Parameter.

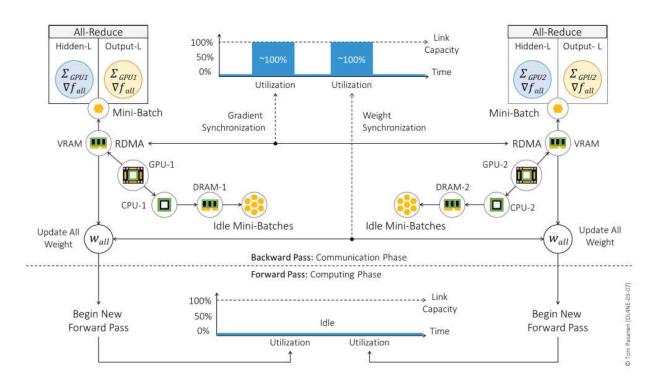

So far, we have explored how the backpropagation algorithm works in multi-class classification using a single GPU. In this section, we examine the scenario where the input dataset exceeds the memory capacity of a single GPU. To handle this, we adopt a data parallelization strategy that splits the training data across multiple GPUs. We also analyze the strategy from a network utilization standpoint.

In Figure 3-7, the training data is divided into mini-batches. The first half of the mini-batches is stored in system memory (DRAM-1) on Server-1, and the second half in system memory (DRAM-2) on Server-2. This setup illustrates a common situation: when the data cannot fully fit into a GPU's VRAM, inactive mini-batches remain in system memory and are

transferred as needed. Meanwhile, the active mini-batch and the model weights are loaded into the GPU's VRAM.

In our example, each mini-batch contains 64 grayscale images, each of size 32 × 32 pixels, meaning 1,024 input features per image. The first hidden layer contains 128 neurons, and the output layer contains 10 neurons.

The total number of weight parameters is as follows:

• Input to hidden layer:

64 images × 128 neurons × 1,024 inputs = **8,388,608 weights**

Hidden to output layer:

128 neurons × 10 neurons = 1,280 weights

• Bias weights:

128 (hidden layer) + 10 (output layer) = 138 bias values

Once the forward pass (computation phase) is complete, the backward pass begins. In this phase, gradients are computed for all neurons using the backpropagation algorithm.

To synchronize gradients across GPUs, we use the All-Reduce collective communication model (detail explanation in chapter 14), which aggregates gradients from each GPU and ensures that all GPUs have consistent copies of the model. In our multi-server setup, this synchronization takes place over the network using Remote Direct Memory Access (RDMA), a mechanism that allows one server's GPU to access another server's GPU memory

directly, bypassing CPU intervention and avoiding the traditional network stack. This form of RDMA (typically via RoCE or InfiniBand, explained in detail in chapter 9) is essential for minimizing latency and maximizing throughput across the cluster.

During gradient synchronization, the GPU's network interface controller (NIC) transmits data at line rate, often resulting in close to 100% link utilization. Once synchronization is complete, each GPU averages the gradients and computes updated weight values.

After the weights are updated, the next mini-batch is loaded into VRAM and training continues. During the compute-intensive forward and backward passes, network utilization is low, as most operations are local

to the GPU. When all GPUs are within the same server, high-speed interconnects like NVLink are typically used to facilitate fast GPU-to-GPU communication. We will cover intra-server memory transfers and their performance impact in a later chapter.

Given that model training can span days to weeks, it is critical that interGPU communication, particularly across servers, is lossless and capable of sustaining line-rate performance. To protect against training loss from network issues, regular checkpoints (snapshots of model weights) should be taken. Even a single dropped packet during gradient exchange could cause the model to diverge or the job to fail, requiring a complete restart.

Figure 3-7: Gradient Synchronization and Network Utilization.

## **REFERENCES**

- [1] Magnus Ekman, "Learning Deep Learning: Theory and Practice of Neural Networks, Computer Vision, Natural Language Processing, and Transformers Using TensorFlow", 17 Aug. 2021

- [2] Yann LeCun, Corina Cortes, Christoper J.C. Burges: The MNIST database of handwritten digits. October 2010.

### https://www.lri.fr/~marc/Master2/MNIST\_doc.pdf

[3] Lima, M. D. P., Giraldi, G. A., & Miranda Junior, G. F. (2023, November 10). Image Classification Using Combination of Topological Features and Neural Networks. arXiv preprint arXiv:2311.06375.

https://arxiv.org/abs/2311.06375

42 Chapter 3: Multi-Class Classification

# CHAPTER 4: CONVOLUTIONAL NEURAL NETWORKS

## INTRODUCTION

The previous chapter explained how Feed-forward Neural Networks (FNNs) can be used for multi-class classification of 28 x 28 pixel handwritten digits from the MNIST dataset. While FNNs work well for this type of task, they have significant limitations when dealing with larger, high-resolution color images.

In neural network terminology, each RGB value of an image is treated as an input feature. For instance, a high-resolution 600 dpi RGB color image with dimensions 3.937 x 3.937 inches contains approximately 5.58 million pixels, resulting in roughly 17 million RGB values.

If we use a fully connected FNN for training, all these 17 million input values are fed into every neuron in the first hidden layer. Each neuron must compute a weighted sum based on these 17 million inputs. The memory required for storing the weights depends on the numerical precision format used. For example, using the 16-bit floating-point (FP16) format, each weight requires 2 bytes. Thus, the memory requirement per neuron would be approximately 32 MB. If the first hidden layer has 10,000 neurons, the total memory required for storing the weights in this layer would be around 316 GB.

In contrast, Convolutional Neural Networks (CNNs) use shared weight matrices called kernels (or filters) across all neurons within a convolutional layer. For example, if we use a  $3 \times 3$  kernel, there are only 9 weights per color channel. This reduces memory usage and computational costs significantly during both the forward and backward passes.

Another limitation of FNNs for image recognition is that they treat each pixel as an independent unit. As a result, FNNs do not capture the spatial relationships between pixels, making them unable to recognize the same object if it shifts within the frame. Additionally, FNNs cannot detect edges or other important features. On the other hand, CNNs have a property called translation invariance, which allows the model to recognize patterns even if they are slightly shifted (small translations along the x and y axes). This helps CNNs classify objects more accurately. Furthermore, CNNs are more robust to minor rotations or scale changes, though they may still require data augmentation or specialized network architectures to handle more complex transformations.

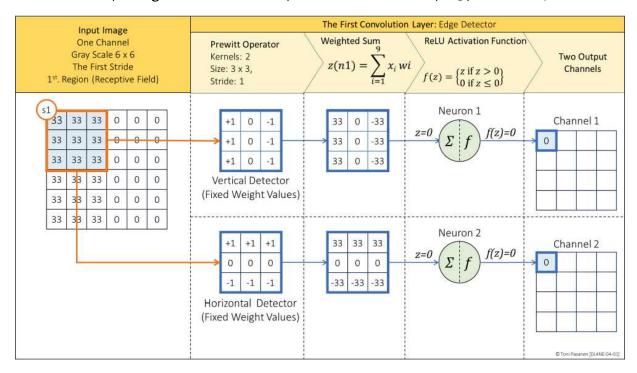

## **CONVOLUTION LAYER**

## **Convolution Process**

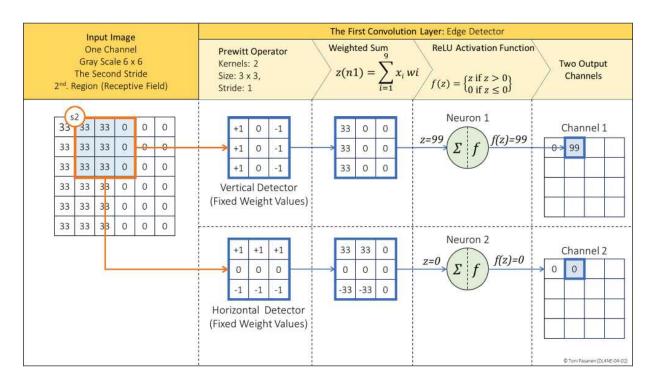

The purpose of the convolution process is to extract features from the image and reduce the number of input parameters before passing them through fully-connected layers. The convolution operation uses a shared weight matrix called kernels or filters, which are shared across all neurons within a convolutional layer. In this example, we use the Prewitt operator, which consists of two 3 x 3 kernels with fixed weight values for detecting vertical and horizontal edges.

In the first step, these two kernels are positioned over the first region of the input image, and each pixel value is multiplied by the corresponding kernel weight. Next, the process computes the weighted sum, z=0, and the result is passed through the ReLU activation function. The resulting activation values, ff(zz)=0, contribute to the neuron-based output channels.

Since our input image is a grayscale image without color channels (unlike an RGB image), it has only one input channel. By using two kernels, we obtain two output channels: one for detecting vertical edges and the other for detecting horizontal edges. The formula for calculating the size of the output channel:

Height = (Image h - Kernel h)/Stride + bias = (6-3)/1 + 1 = 4

### Width = (Image w - Kernel w)/Stride + bias = (6-3)/1 + 1 = 4

Figure 4-1: Convolution Layer – Stride One.

After calculating the first value for the output channel using the image values in the first region, the kernel is shifted one step to the right (stride of 1) to cover the next region. The convolution process calculates the weighted sum based on the values in this region and the weights of the kernel. The result is then passed through the ReLU activation function. The output of the ReLU activation function differs for the first output channel, it is ff(z)=99; for the second output channel, it is ff(z)=0.

Figure 4-2: Convolution Layer – Stride Two.

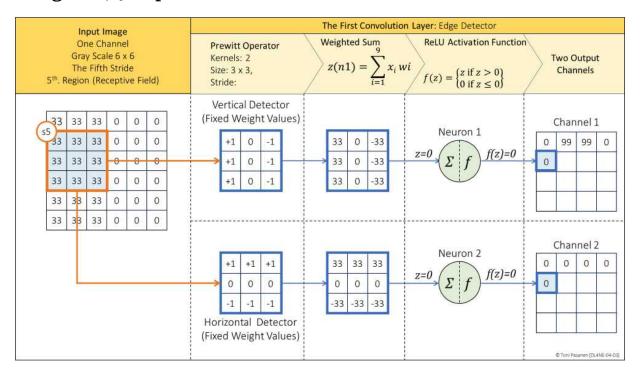

Figure 4-3 depicts the fifth stride.

Figure 4-3: Convolution Layer – Stride Five.

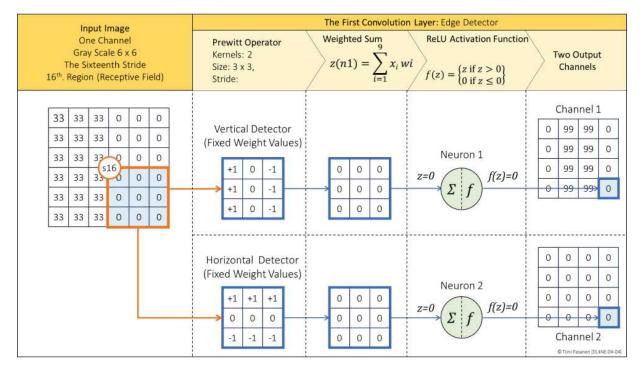

The sixteenth stride, shown in Figure 4-4, is the last one. Now output channels one and two are filled.

Figure 4-4: Convolution Layer – Stride Sixteenth.

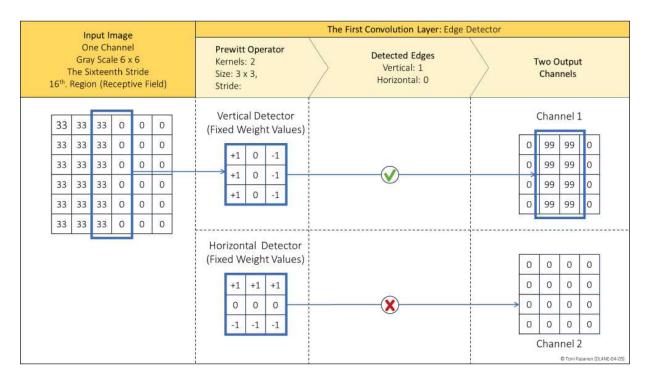

Figure 4-5 shows how the convolution process found one vertical edge and zero horizontal edge from the input image. The convolution process produces two output channels, each with a size of  $4 \times 4$  pixels, while the original input image was  $6 \times 6$  pixels.

Figure 4-5: Convolution Layer – Detected Edges

# **MaxPooling**

MaxPooling is used to reduce the size of the output channels if needed. In our example, where the channel size is relatively small  $(4 \times 4)$ , MaxPooling is unnecessary, but we use it here to demonstrate the process. Similar to convolution, MaxPooling uses a kernel and a stride. However, instead of fixed weights associated with the kernel, MaxPooling selects the highest value from each covered region. This means there is no computation involved in creating the new matrix. MaxPooling can be considered as a layer or part of the convolution layer. Due to its non-computational nature, I see it as part of the convolution layer rather than a separate layer.

Figure 4-6: Convolution Layer: MaxPooling

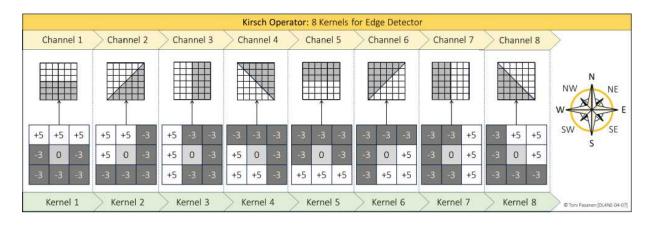

# The First Convolution Layer: Convolution

In this section, we take a slightly different view of convolutional neural networks compared to the preceding sections. In this example, we use the Kirsch operator in the first convolution layer. It uses 8 kernels for detecting vertical, horizontal, and diagonal edges. Similar to the Prewitt operator, the

Kirsch operator uses fixed weight values in its kernels. These values are

shown in Figure 4-7.

Figure 4-7: Kirsch Operator.

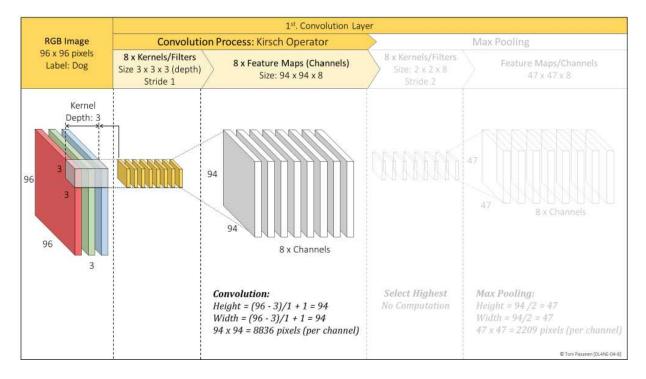

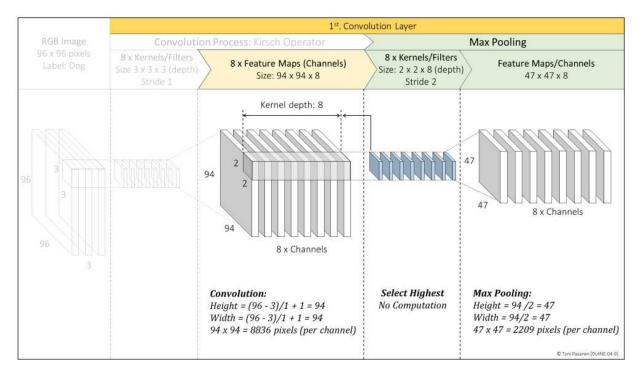

In Figure 4-8, we use a pre-labeled 96 x 96 RGB image for training. An RGB image has three color channels: red, green, and blue for each pixel. It is possible to apply all kernels to each color channel individually, resulting in  $3 \times 8 = 24$  output channels. However, we follow the common practice of applying the kernels to all input channels simultaneously, meaning the eight Kirsch kernels have a depth of 3 (matching the RGB channels). Each kernel processes the RGB values together and produces one output channel. Thus, each neuron uses 3 (width) x 3 (height) x 3 (depth) = 27 weight parameters for calculating the weighted sum. With a stride value of one, the convolution process generates eight 94 x 94 output channels. The formula for calculating weighted sum:

```

3

zz=^

ww=1

33

```

^ (iiiiiiiii [ww, h, dd] xx kkiikkkkiikk [ww, h, dd]) + yyiiiibb h=1 dd=1

Figure 4-8: The First Convolution Layer – Convolution Process.

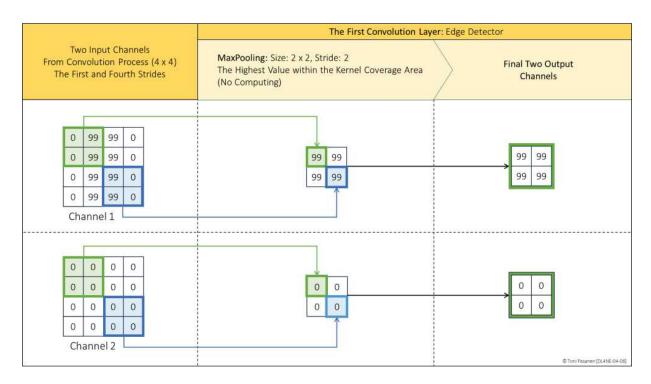

# The First Convolution Layer: MaxPooling

To reduce the size of the output channels from the first convolution layer, we use MaxPooling. We apply eight 2 x 2 kernels, each with a depth of 8, corresponding to the output channels. All kernels process the channels simultaneously, selecting the highest value among the eight channels. MaxPooling with this setting reduces the size of each output channel by half, resulting in eight 47 x 47 output channels, which are then used as input channels for the second convolution layer.

Figure 4-9: The First Convolution Layer – MaxPooling.

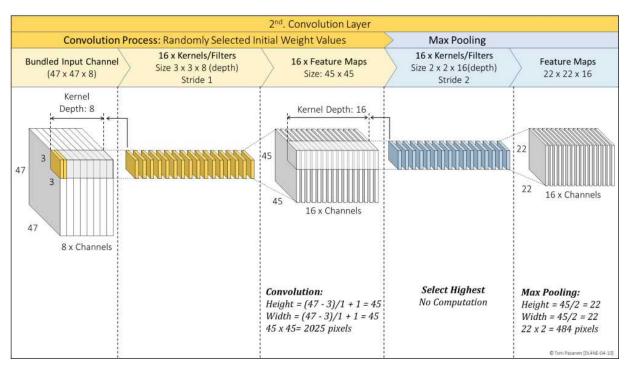

# The Second Convolution Layer

Figure 4-10 shows both the convolution and MaxPooling processes. The eight  $47 \times 47$  output channels produced by the first convolution layer are used as input channels for the second convolution layer. In this layer, we use 16 kernels whose initial weight values are randomly selected and adjusted during the training process. The kernel size is set to  $3 \times 3$ , and the depth is 8, corresponding to the number of input channels. Thus, each kernel calculates a weighted sum over  $3 \times 3 \times 8 = 72$  parameters with 72 weight values. All 16 kernels produce new  $45 \times 45$  output channels by applying the ReLU activation function. Before flattening the output channels, our model applies a MaxPooling operation, which selects the highest value within the kernel

coverage area (region). This reduces the size of the output channels by half, from  $45 \times 45$  to  $22 \times 22$ .

If we had used the original image without convolutional processing as input to the fully connected layer, there would have been 27,648 input parameters (96 x 96 x 3). Thus, the two convolution layers reduce the number of input parameters to 7,744 (22 x 22 x 16), which is approximately a 72% reduction.

**Figure 4-10:** The Second Convolution Layer – Convolution and MaxPooling.

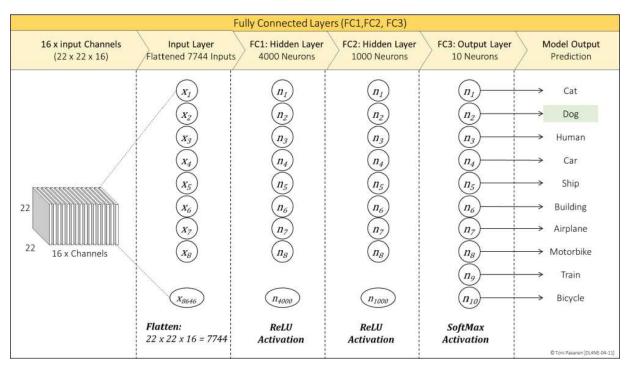

## **FULLY CONNECTED LAYERS**

Before feeding the data into the fully connected layer, the multidimensional 3D array (3D tensor) is converted into a 1D vector. This produces 7,744 input values ( $22 \times 22 \times 16$ ) for the input layer. We use 4,000 neurons with the ReLU activation function in the first hidden layer, which is approximately half the number of input values. In the second hidden layer, we have 1,000 neurons with the ReLU function. The last layer, the output layer, has 10 neurons using the SoftMax function.

Figure 4-11: Fully Connected Layer – Convolution and MaxPooling.

## **BACKPROPAGATION PROCESS**

In Fully Connected Neural Networks (FCNNs), every neuron has its own unique set of weights. In contrast, Convolutional Neural Networks (CNNs) use parameter sharing, where the same filter (kernel) is applied across the entire input image. This approach not only reduces the number of parameters but also enhances efficiency.

Additionally, backpropagation in CNNs preserves the spatial structure <sup>1</sup> of the input data through convolution and pooling operations. This helps the network learn spatial features like edges, textures, and patterns. In contrast, FNNs flatten the input data into a 1D vector, losing any spatial information and making it harder to capture meaningful patterns in images.

### **REFERENCES**

- [1] Magnus Ekman, "Learning Deep Learning: Theory and Practice of Neural Networks, Computer Vision, Natural Language Processing, and Transformers Using TensorFlow", 17 Aug. 2021

- [2] Yann LeCun, Corina Cortes, Christoper J.C. Burges: The MNIST database of handwritten digits. October 2010.

## https://www.lri.fr/~marc/Master2/MNIST\_doc.pdf

[3] Goodfellow, I., Bengio, Y., & Courville, A. (2016, November 18). Deep Learning. MIT Press.

### https://www.deeplearningbook.org/

[4] IBM. (n.d.). What are Convolutional Neural Networks?

<u>https://www.ibm.com/think/topics/convolutional-neural-networks</u>

- [5] Wikipedia contributors. (n.d.). Kirsch operator. Wikipedia. <a href="https://en.wikipedia.org/wiki/Kirsch operator">https://en.wikipedia.org/wiki/Kirsch operator</a>

- [6] Wikipedia contributors. (n.d.). Prewitt operator. Wikipedia.

## https://en.wikipedia.org/wiki/Prewitt\_operator

56 Chapter 4: Convolutional Neural Networks

1

Spatial features refer to the characteristics of an image that describe the relationship between pixels based on their positions. These features capture the spatial structure of the image, such as edges, corners, textures, shapes, and patterns, which are essential for recognizing objects and understanding the visual content.

# CHAPTER 5: RECURRENT NEURAL NETWORKS

## INTRODUCTION

So far, this book has introduced two neural network architectures. The first one, the Feed-Forward Neural Network (FNN), works well for simple tasks, such as recognizing handwritten digits in small-sized images. The second one, the Convolutional Neural Network (CNN), is designed for processing larger images. CNNs can identify objects in images even when the location or orientation of the object changes.

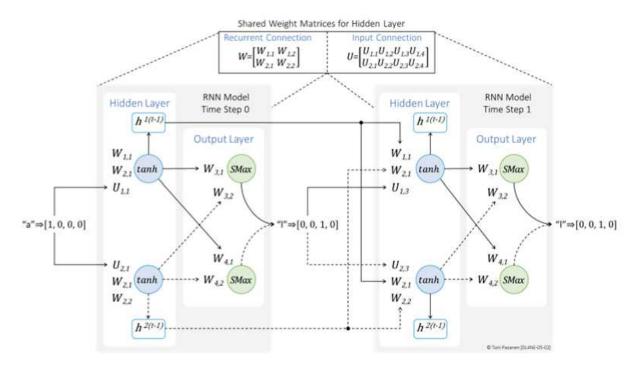

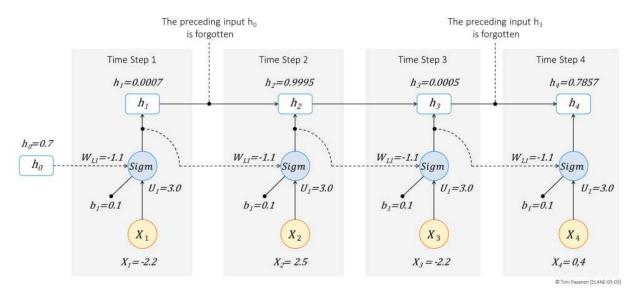

This chapter introduces the Recurrent Neural Network (RNN). Unlike FNNs and CNNs, an RNN's inputs include not only the current data but also all the inputs it has processed previously. In other words, an RNN preserves and uses historical data. This is achieved by feeding the output of the previous time step back into the hidden layer along with the current input vector.

Although RNNs can be used for predicting sequential data of variable lengths, such as sales figures or a patient's historical health records, this chapter focuses on how RNNs can perform character-based text autocompletion. The upcoming chapters will explore word-based text prediction.

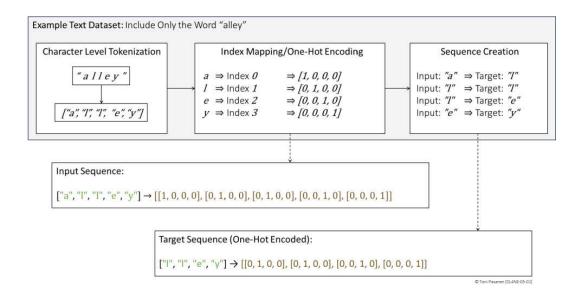

#### TEXT DATASETS

For training the RNN model, we typically use text datasets like IMDB Reviews or the Wikipedia Text Corpus. However, in this chapter, we simplify the process by using a tailored dataset containing only the word "alley". Figure 5-1 illustrates the steps involved.

- 1. Splitting the text into characters: First, we break the word into its individual letters (e.g., a, l, l, e, y).